# FM25Q08A 8M-BIT SERIAL FLASH MEMORY

| Datasneet |  |  |  |

|-----------|--|--|--|

|           |  |  |  |

|           |  |  |  |

Nov. 2017

INFORMATION IN THIS DOCUMENT IS INTENDED AS A REFERENCE TO ASSIST OUR CUSTOMERS IN THE SELECTION OF SHANGHAI FUDAN MICROELECTRONICS GROUP CO., LTD PRODUCT BEST SUITED TO THE CUSTOMER'S APPLICATION; THEY DO NOT CONVEY ANY LICENSE UNDER ANY INTELLECTUAL PROPERTY RIGHTS, OR ANY OTHER RIGHTS, BELONGING TO SHANGHAI FUDAN MICROELECTRONICS GROUP CO., LTD OR A THIRD PARTY.

WHEN USING THE INFORMATION CONTAINED IN THIS DOCUMENTS, PLEASE BE SURE TO EVALUATE ALL INFORMATION AS A TOTAL SYSTEM BEFORE MAKING A FINAL DECISION ON THE APPLICABILITY OF THE INFORMATION AND PRODUCTS.

PURCHASERS ARE SOLELY RESPONSIBLE FOR THE CHOICE, SELECTION AND USE OF THE SHANGHAI FUDAN MICROELECTRONICS GROUP CO., LTD PRODUCTS AND SERVICES DESCRIBED HEREIN, AND SHANGHAI FUDAN MICROELECTRONICS GROUP CO., LTD ASSUMES NO LIABILITY WHATSOEVER RELATING TO THE CHOICE, SELECTION OR USE OF THE SHANGHAI FUDAN MICROELECTRONICS GROUP CO., LTD PRODUCTS AND SERVICES DESCRIBED HEREIN. UNLESS EXPRESSLY APPROVED IN WRITING BY AN AUTHORIZED SHANGHAI FUDAN MICROELECTRONICS GROUP CO., LTD REPRESENTATIVE, SHANGHAI FUDAN MICROELECTRONICS GROUP CO., LTD PRODUCTS ARE NOT RECOMMENDED, AUTHORIZED OR WARRANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING APPLICATIONS, NOR IN PRODUCTS OR SYSTEMS WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJURY, DEATH, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE.

FUTURE ROUTINE REVISIONS WILL OCCUR WHEN APPROPRIATE, WITHOUT NOTICE. CONTACT SHANGHAI FUDAN MICROELECTRONICS GROUP CO., LTD SALES OFFICE TO OBTAIN THE LATEST SPECIFICATIONS AND BEFORE PLACING YOUR PRODUCT ORDER. PLEASE ALSO PAY ATTENTION TO INFORMATION PUBLISHED BY SHANGHAI FUDAN MICROELECTRONICS GROUP CO., LTD BY VARIOUS MEANS, INCLUDING SHANGHAI FUDAN MICROELECTRONICS GROUP CO., LTD HOME PAGE (HTTP://WWW.FMSH.COM/).

PLEASE CONTACT SHANGHAI FUDAN MICROELECTRONICS GROUP CO., LTD LOCAL SALES OFFICE FOR THE SPECIFICATION REGARDING THE INFORMATION IN THIS DOCUMENT OR SHANGHAI FUDAN MICROELECTRONICS GROUP CO., LTD PRODUCTS.

### **Trademarks**

Shanghai Fudan Microelectronics Group Co., Ltd name and logo, the "复旦" logo are trademarks or registered trademarks of Shanghai Fudan Microelectronics Group Co., Ltd or its subsidiaries in China.

Shanghai Fudan Microelectronics Group Co., Ltd, Printed in the China, All Rights Reserved.

Shanghai Fudan Microelectronics Group Company Limited -

# 1. Description

The FM25Q08A is a 8M-bit (1M-byte) Serial Flash with advanced write mechanisms. The FM25Q08A supports Peripheral standard Serial Interface Dual/Quad I/O as well as 2-clock instruction cycle Quad Peripheral Interface (QPI). They are ideal for code shadowing to RAM, executing code directly from Dual/Quad SPI (XIP) and storing voice, text and data.

The FM25Q08A can be programmed 1 to 256 bytes at a time, using the Page Program instruction. It is designed to allow either single Sector/Block at a time or full chip erase operation. The FM25Q08A can be configured to protect part of the memory as the software protected mode. The device can sustain a minimum of 100K program/erase cycles on each sector or block.

# 2. Features

### • 8Mbit of Flash memory

- 256 uniform sectors with 4K-byte each

- 16 uniform blocks with 64K-byte each or

- 32 uniform blocks with 32K-byte each

- 256 bytes per programmable page

#### Wide Operation Range

- 2.3V~3.6V single voltage supply

- Industrial temperature range

#### Serial Interface

- Standard SPI: CLK, CS#, DI, DO, WP#

- Dual SPI: CLK, CS#, DQ<sub>0</sub>, DQ<sub>1</sub>, WP#

- Quad SPI: CLK, CS#, DQ<sub>0</sub>, DQ<sub>1</sub>, DQ<sub>2</sub>, DQ<sub>3</sub>

- QPI: CLK, CS#, DQ<sub>0</sub>, DQ<sub>1</sub>, DQ<sub>2</sub>, DQ<sub>3</sub>

- Continuous READ mode support

- Allow true XIP (execute in place) operation

#### High Performance

- Max FAST READ clock frequency: 104MHz

- Dual I/O Data transfer up to 208Mbits/s

- Quad I/O Data transfer up to 416Mbits/s

- Typical page program time: 0.5ms

- Typical sector erase time: 50ms

- Typical block erase time: 120/150ms

- Typical chip erase time: 2.5s

### Low Power Consumption

Typical standby current: 1µA

#### Security

- Software and hardware write protection

- Lockable 2X512-Byte OTP security sectors

- 64-Bit Unique ID for each device

- Discoverable parameters(SFDP) register

### High Reliability

- Endurance: 100,000 program/erase cycles

- Data retention: 20 years

### Green Package

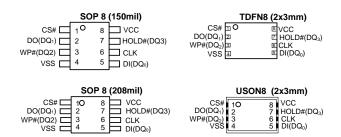

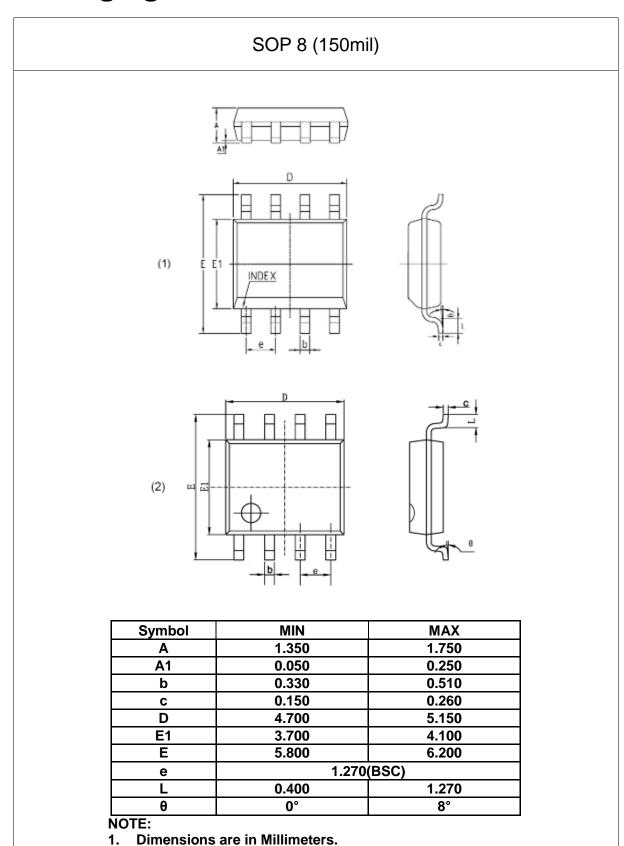

- 8-pin SOP (150mil)

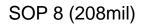

- 8-pin SOP (208mil)

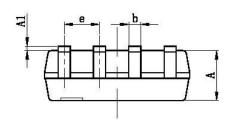

- 8-pin TDFN (2x3mm)

- 8-pin USON8 (2x3mm)

- All Packages are RoHS Compliant and Halogenfree

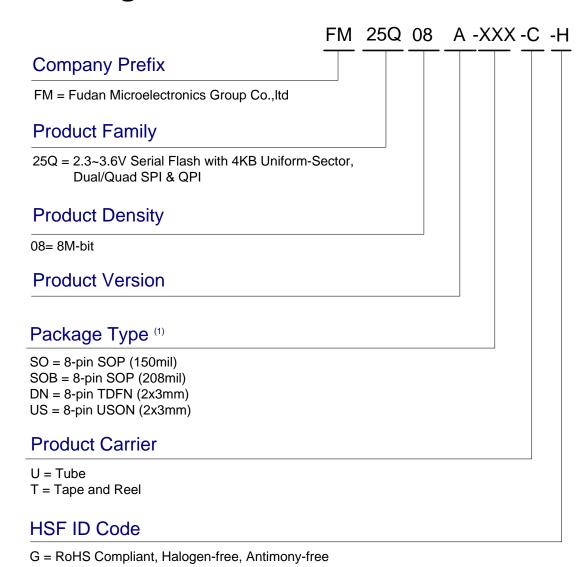

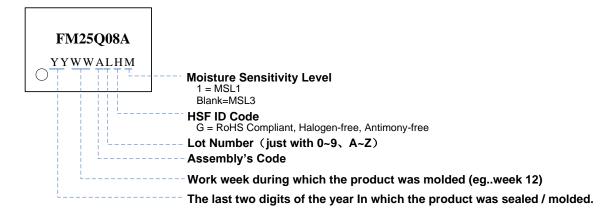

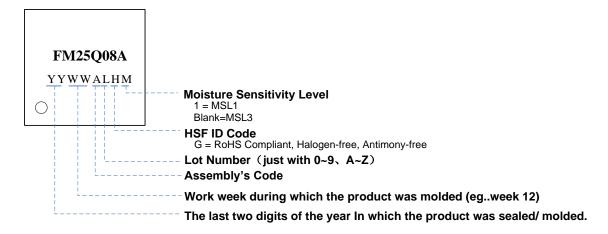

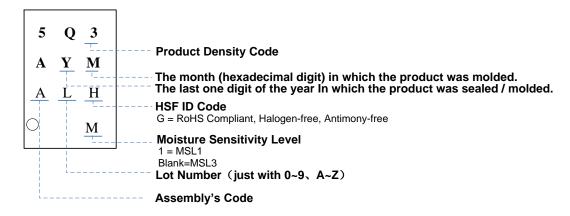

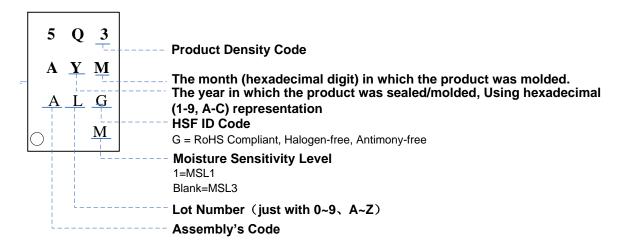

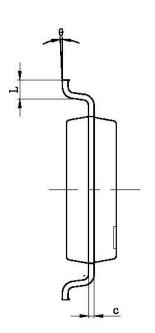

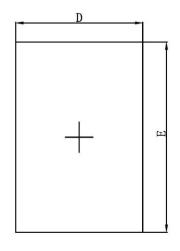

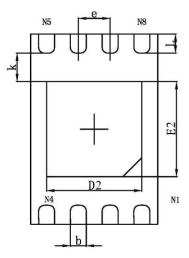

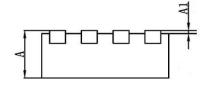

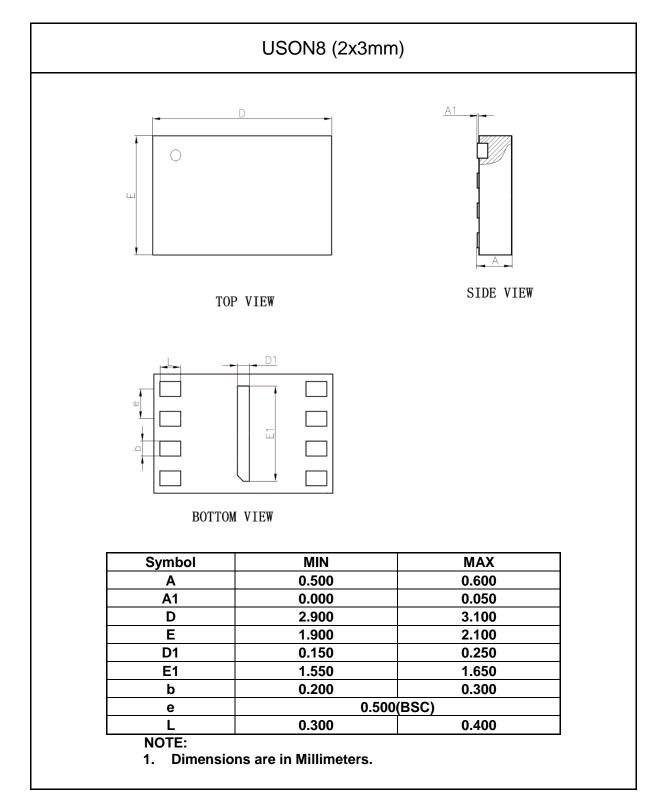

# 3. Packaging Type

# 4. Pin Configurations

| PIN<br>NO. | PIN<br>NAME                 | I/O | FUNCTION                                                 |

|------------|-----------------------------|-----|----------------------------------------------------------|

| 1          | CS#                         | I   | Chip Select Input                                        |

| 2          | DO<br>(DQ <sub>1</sub> )    | I/O | Data Output (Data Input Output 1) <sup>(1)</sup>         |

| 3          | WP#<br>(DQ <sub>2</sub> )   | I/O | Write Protect Input (Data Input Output 2) <sup>(2)</sup> |

| 4          | VSS                         |     | Ground                                                   |

| 5          | DI<br>(DQ <sub>0</sub> )    | I/O | Data Input (Data Input Output 0) <sup>(1)</sup>          |

| 6          | CLK                         |     | Serial Clock Input                                       |

| 7          | HOLD#<br>(DQ <sub>3</sub> ) | I/O | Hold Input (Data Input Output 3) <sup>(2)</sup>          |

| 8          | VCC                         |     | Power Supply                                             |

#### Note:

- 1 DQ<sub>0</sub> and DQ<sub>1</sub> are used for Dual SPI instructions.

- 2 DQ<sub>0</sub> DQ<sub>3</sub> are used for Quad SPI and QPI instructions.

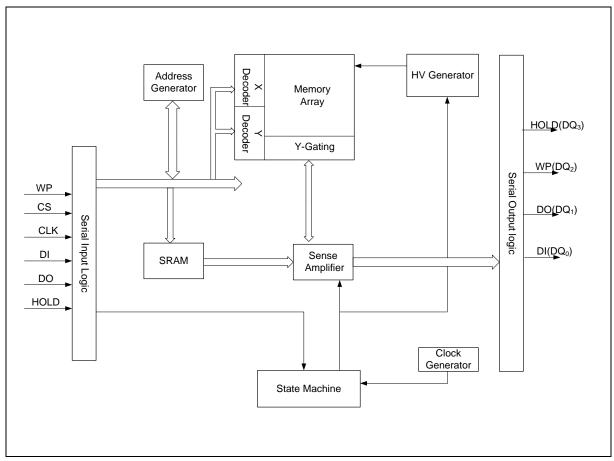

# 5. Block Diagram

Figure 1 FM25Q08A Serial Flash Memory Block Diagram

# 6. Pin Descriptions

**Serial Clock (CLK):** The SPI Serial Clock Input (CLK) pin provides the timing for serial input and output operations.

**Serial Data Input, Output and I/Os (DI, DO and DQ<sub>0</sub>, DQ<sub>1</sub>, DQ<sub>2</sub>, DQ<sub>3</sub>):** The FM25Q08A supports standard SPI, Dual SPI, Quad SPI and QPI operation. Standard SPI instructions use the unidirectional DI (input) pin to serially write instructions, addresses or data to the device on the rising edge of the Serial Clock (CLK) input pin. Standard SPI also uses the unidirectional DO (output) to read data or status from the device on the falling edge of CLK.

Dual/Quad SPI and QPI instructions use the bidirectional DQ pins to serially write instructions, addresses or data to the device on the rising edge of CLK and read data or status from the device on the falling edge of CLK. Quad SPI and QPI instructions require the non-volatile Quad Enable bit (QE) in Status Register-2 to be set. When QE=1, the WP# pin becomes DQ<sub>2</sub> and HOLD# pin becomes DQ<sub>3</sub>.

Chip Select (CS#): The SPI Chip Select (CS#) pin enables and disables device operation. When CS# is high, the device is deselected and the Serial Data Output (DO, or DQ<sub>0</sub>, DQ<sub>1</sub>, DQ<sub>2</sub>, DQ<sub>3</sub>) pins are at high impedance. When deselected, the devices power consumption will be at standby levels unless an internal erase, program or write status register cycle is in progress. When CS# is brought low, the device will be selected, power consumption will increase to active levels and instructions can be written to and data read from the device. After power-up, CS# must transition from high to low before a new instruction will be accepted. The CS# input must track the VCC supply level at power-up (see "9 Write Protection" and Figure 64). If needed a pull-up resister on CS# can be used to accomplish this.

**HOLD (HOLD#):** The HOLD# pin allows the device to be paused while it is actively selected. When HOLD# is brought low, while CS# is low, the DO pin will be at high impedance and signals on the DI and CLK pins will be ignored (don't care). When HOLD# is brought high, device operation can resume. The HOLD# function can be useful when multiple devices are sharing the same SPI signals. The HOLD# pin is active low. When the QE bit of Status Register-2 is set for Quad I/O, the HOLD# pin function is not available since this pin is used for DQ<sub>3</sub>.

**Write Protect (WP#):** The Write Protect (WP#) pin can be used to prevent the Status Registers from being written. Used in conjunction with the Status Register's Block Protect (CMP, SEC, TB, BP2, BP1 and BP0) bits and Status Register Protect (SRP) bits, a portion as small as a 4KB sector or the entire memory array can be hardware protected. The WP# pin is active low. However, when the QE bit of Status Register-2 is set for Quad I/O, the WP# pin function is not available since this pin is used for DQ<sub>2</sub>.

# 7. Memory Organization

The FM25Q08A array is organized into 4,096 programmable pages of 256-bytes each. Up to 256 bytes can be programmed (bits are programmed from 1 to 0) at a time. Pages can be erased in groups of 16 (4KB sector erase), groups of 128 (32KB block erase), groups of 256 (64KB block erase) or the entire chip (chip erase). The FM25Q08A has 256 erasable sectors, 32 erasable 32-k byte blocks and 16 erasable 64-k byte blocks respectively. The small 4KB sectors allow for greater flexibility in applications that require data and parameter storage.

**Table 1** Memory Organization

| Group<br>(512KB) | Block<br>(64KB) | Block<br>(32KB) | Sector<br>(4KB) | Address            | s Range                |

|------------------|-----------------|-----------------|-----------------|--------------------|------------------------|

|                  |                 | 31              | 255             | 0FF000h            | 0FFFFFh                |

|                  | 15              | 1               |                 |                    |                        |

|                  |                 | 30              | 240             | 0F0000h            | 0F0FFFh                |

|                  |                 | 29              | 239             | 0EF000h            | 0EFFFFh                |

|                  | 14              | I               |                 |                    |                        |

|                  |                 | 28              | 224             | 0E0000h            | 0E0FFFh                |

|                  |                 | 27              | 223             | 0DF000h            | 0DFFFFh                |

|                  | 13              | I               |                 |                    |                        |

|                  |                 | 26              | 208             | 0D0000h            | 0D0FFFh                |

|                  |                 | 25              | 207             | 0CF000h            | 0CFFFFh                |

|                  | 12              | I               |                 | •••                |                        |

| 1                |                 | 24              | 192             | 0C0000h            | 0C0FFFh                |

| •                |                 | 23              | 191             | 0BF000h            | 0BFFFFh                |

|                  | 11              | I               |                 | •••                | •••                    |

|                  |                 | 22              | 176             | 0B0000h            | 0B0FFFh                |

|                  |                 | 21              | 175             | 0AF000h            | 0AFFFFh                |

|                  | 10              | I               |                 |                    | •••                    |

|                  |                 | 20              | 160             | 0A0000h            | 0A0FFFh                |

|                  | _               | 19              | 159             | 09F000h            | 09FFFFh                |

|                  | 9               |                 |                 |                    |                        |

|                  |                 | 18              | 144             | 090000h            | 090FFFh                |

|                  | _               | 17              | 143             | 08F000h            | 08FFFFh                |

|                  | 8               |                 |                 |                    |                        |

|                  |                 | 16              | 128             | 080000h            | 080FFFh                |

|                  | 7               | 15              | 127             | 07F000h            | 07FFFFh                |

|                  | 7               | <br>  14        | 112             | 070000h            | <br>070FFFh            |

|                  |                 |                 | 111             | 070000h<br>06F000h | 070FFFh<br>06FFFFh     |

|                  | 6               | 13<br>I         |                 |                    |                        |

| 0                |                 | <br>  12        | 96              | 060000h            | 060FFFh                |

|                  |                 |                 | 95              | 05F000h            | 05FFFFh                |

|                  | 5               | 11<br>I         |                 |                    |                        |

|                  | 5               | 10              | 80              | 050000h            | <br>050FFFh            |

|                  | 4               | 9               | 79              | 030000H            | 04FFFFh                |

|                  | 7               | J               | 13              | U-11 00011         | U <del>-1</del> 111111 |

| Group<br>(512KB) | Block<br>(64KB) | Block<br>(32KB) | Sector<br>(4KB) | Addres  | Address Range |  |  |

|------------------|-----------------|-----------------|-----------------|---------|---------------|--|--|

|                  |                 | I               |                 |         |               |  |  |

|                  |                 | 8               | 64              | 040000h | 040FFFh       |  |  |

|                  |                 | 7               | 63              | 03F000h | 03FFFFh       |  |  |

|                  | 3               | I               |                 |         |               |  |  |

|                  |                 | 6               | 48              | 030000h | 030FFFh       |  |  |

|                  |                 | 5               | 47              | 02F000h | 02FFFFh       |  |  |

|                  | 2               | I               |                 |         |               |  |  |

|                  |                 | 4               | 32              | 020000h | 020FFFh       |  |  |

|                  |                 | 3               | 31              | 01F000h | 01FFFFh       |  |  |

|                  | 1               | l               |                 |         |               |  |  |

|                  |                 | 2               | 16              | 010000h | 010FFFh       |  |  |

|                  |                 |                 | 15              | 00F000h | 00FFFFh       |  |  |

|                  |                 | 1               |                 |         |               |  |  |

|                  | 0               | I               | 2               | 002000h | 002FFFh       |  |  |

|                  |                 | Ö               | 1               | 001000h | 001FFFh       |  |  |

|                  |                 |                 | 0               | 000000h | 000FFFh       |  |  |

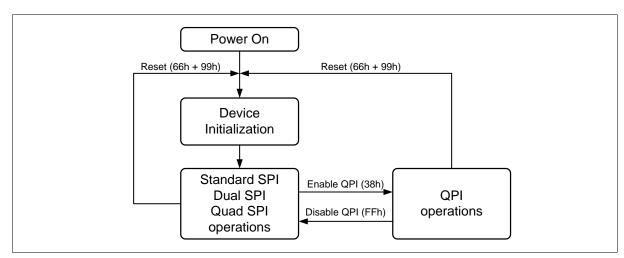

# 8. Device Operations

Figure 2 FM25Q08A Serial Flash Memory Operation Diagram

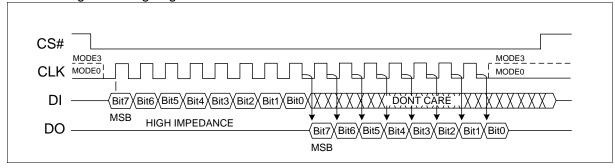

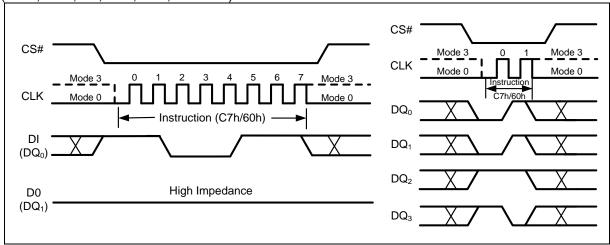

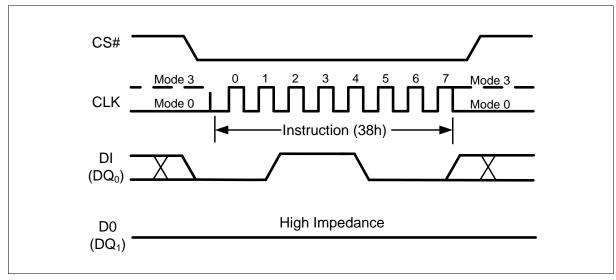

### 8.1. Standard SPI

The FM25Q08A is accessed through an SPI compatible bus consisting of four signals: Serial Clock (CLK), Chip Select (CS#), Serial Data Input (DI) and Serial Data Output (DO). Standard SPI instructions use the DI input pin to serially write instructions, addresses or data to the device on the rising edge of CLK. The DO output pin is used to read data or status from the device on the falling edge of CLK.

SPI bus operation Mode 0 (0,0) and 3 (1,1) are supported. The primary difference between Mode 0 and Mode 3 concerns the normal state of the CLK signal when the SPI bus master is in standby and data is not being transferred to the Serial Flash. For Mode 0, the CLK signal is normally low on the falling and rising edges of CS#. For Mode 3, the CLK signal is normally high on the falling and rising edges of CS#.

Figure 3 The difference between Mode 0 and Mode 3

### 8.2. Dual SPI

The FM25Q08A supports Dual SPI operation when using instructions such as "Fast Read Dual Output (3Bh)" and "Fast Read Dual I/O (BBh)". These instructions allow data to be transferred to or from the device at two to three times the rate of ordinary Serial Flash devices. The Dual SPI Read instructions are ideal for quickly downloading code to RAM upon power-up (code-shadowing) or for executing non-speed- critical code directly from the SPI bus (XIP). When using Dual SPI instructions, the DI and DO pins become bidirectional I/O pins:  $DQ_0$  and  $DQ_1$ .

### 8.3. Quad SPI

The FM25Q08A supports Quad SPI operation when using instructions such as "Fast Read Quad Output (6Bh)", "Fast Read Quad I/O (EBh)", "Word Read Quad I/O (E7h)" and "Octal Word Read Quad I/O (E3h)". These instructions allow data to be transferred to or from the device four to six times the rate of ordinary Serial Flash. The Quad Read instructions offer a significant improvement in continuous and random access transfer rates allowing fast code-shadowing to RAM or execution directly from the SPI bus (XIP). When using Quad SPI instructions the DI and DO pins become bidirectional DQ<sub>0</sub> and DQ<sub>1</sub> and the WP # and HOLD# pins become DQ<sub>2</sub> and DQ<sub>3</sub> respectively. Quad SPI instructions require the non-volatile Quad Enable bit (QE) in Status Register-2 to be set.

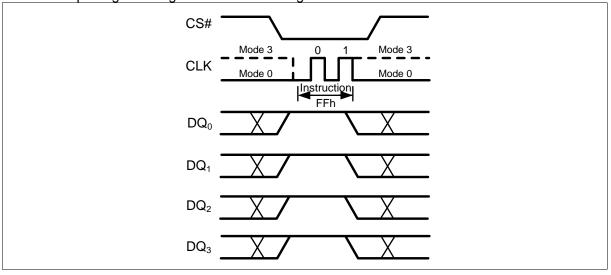

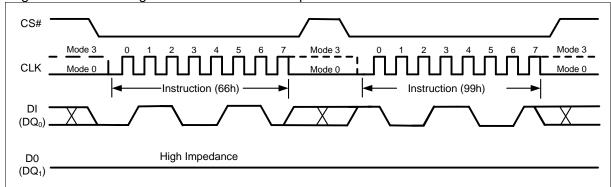

### 8.4. QPI

The FM25Q08A supports Quad Peripheral Interface (QPI) operations only when the device is switched from Standard/Dual/Quad SPI mode to QPI mode using the "Enable QPI (38h)" instruction. The typical SPI protocol requires that the byte-long instruction code being shifted into the device only via DI pin in eight serial clocks. The QPI mode utilizes all four DQ pins to input the instruction code, thus only two serial clocks are required. This can significantly reduce the SPI instruction overhead and improve system performance in an XIP environment. Standard/Dual/Quad SPI mode and QPI mode are exclusive. Only one mode can be active at any given time. "Enable QPI (38h)" and "Disable QPI (FFh)" instructions are used to switch between these two modes. Upon power-up or after a software reset using "Reset (99h)" instruction, the default state of the device is Standard/Dual/Quad SPI mode. To enable QPI mode, the non-volatile Quad Enable bit (QE) in Status Register-2 is required to be set. When using QPI instructions, the DI and DO pins become bidirectional DQ<sub>0</sub> and DQ<sub>1</sub>, and the WP# and HOLD# pins become DQ<sub>2</sub> and DQ<sub>3</sub> respectively. See Figure 2 for the device operation modes.

### 8.5. Hold

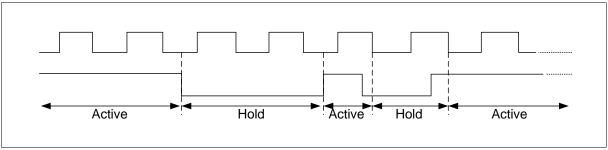

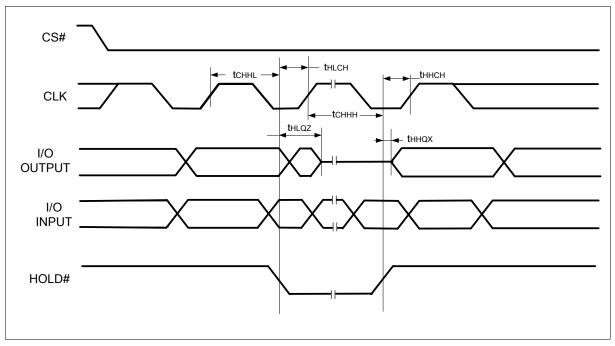

For Standard SPI and Dual SPI operations, the HOLD# signal allows the FM25Q08A operation to be paused while it is actively selected (when CS# is low). The HOLD# function may be useful in cases where the SPI data and clock signals are shared with other devices. For example, consider if the page buffer was only partially written when a priority interrupt requires use of the SPI bus. In this case the HOLD# function can save the state of the instruction and the data in the buffer so programming can resume where it left off once the bus is available again. The HOLD# function is only available for standard SPI and Dual SPI operation, not during Quad SPI or QPI.

To initiate a HOLD# condition, the device must be selected with CS# low. A HOLD# condition will activate on the falling edge of the HOLD# signal if the CLK signal is already low. If the CLK is not already low the HOLD# condition will activate after the next falling edge of CLK. The HOLD# condition will terminate on the rising edge of the HOLD# signal if the CLK signal is already low. If the CLK is not already low the HOLD# condition will terminate after the next falling edge of CLK. During a HOLD# condition, the Serial Data Output (DO) is high impedance, and Serial Data Input (DI) and Serial Clock (CLK) are ignored. The Chip Select (CS#) signal should be kept active (low) for the full duration of the HOLD# operation to avoid resetting the internal logic state of the device.

Figure 4 Hold Condition Waveform

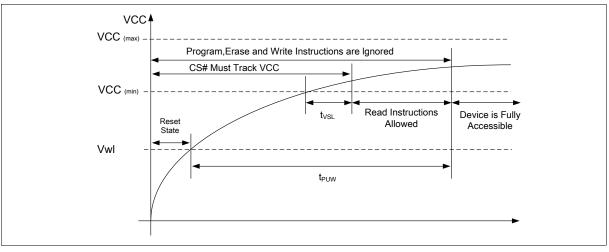

# 9. Write Protection

Applications that use non-volatile memory must take into consideration the possibility of noise and other adverse system conditions that may compromise data integrity. To address this concern, the FM25Q08A provides several means to protect the data from inadvertent writes.

#### **Write Protect Features**

- Device resets when VCC is below threshold

- Time delay write disable after Power-up

- Write enable/disable instructions and automatic write disable after erase or program

- Software and Hardware (WP# pin) write protection using Status Register

- Write Protection using Power-down instruction

- Lock Down write protection for Status Register until the next power-up

- One Time Program (OTP) write protection for array and Security Sectors using Status Register.

Upon power-up or at power-down, the FM25Q08A will maintain a reset condition while VCC is below the threshold value of VWI, (See "12.3 Power-up Timing" and Figure 64). While reset, all operations are disabled and no instructions are recognized. During power-up and after the VCC voltage exceeds VWI, all program and erase related instructions are further disabled for a time delay of  $t_{\text{PUW}}$ . This includes the Write Enable, Page Program, Sector Erase, Block Erase, Chip Erase and the Write Status Register instructions. Note that the chip select pin (CS#) must track the VCC supply level at power-up until the VCC-min level and  $t_{\text{VSL}}$  time delay is reached. If needed a pull-up resister on CS# can be used to accomplish this.

After power-up the device is automatically placed in a write-disabled state with the Status Register Write Enable Latch (WEL) set to a 0. A Write Enable instruction must be issued before a Page Program, Sector Erase, Block Erase, Chip Erase or Write Status Register instruction will be accepted. After completing a program, erase or write instruction the Write Enable Latch (WEL) is automatically cleared to a write-disabled state of 0.

Software controlled write protection is facilitated using the Write Status Register instruction and setting the Status Register Protect (SRP0, SRP1) and Block Protect (CMP, SEC, TB, BP2, BP1 and BP0) bits. These settings allow a portion as small as a 4KB sector or the entire memory array to be configured as read only. Used in conjunction with the Write Protect (WP#) pin, changes to the Status Register can be enabled or disabled under hardware control. See Status Register section for further information. Additionally, the Power-down instruction offers an extra level of write protection as all instructions are ignored except for the Release Power-down instruction.

# 10. Status Register

The Read Status Register instructions can be used to provide status on the availability of the Flash memory array, if the device is write enabled or disabled, the state of write protection, Quad SPI setting, Security Sector lock status. The Write Status Register instruction can be used to configure the device write protection features, Quad SPI setting and Security Sector OTP lock. Write access to the Status Register is controlled by the state of the non-volatile Status Register Protect bits (SRP0, SRP1), the Write Enable instruction, and during Standard/Dual SPI operations, the WP# pin.

Factory default for all Status Register bits are 0.

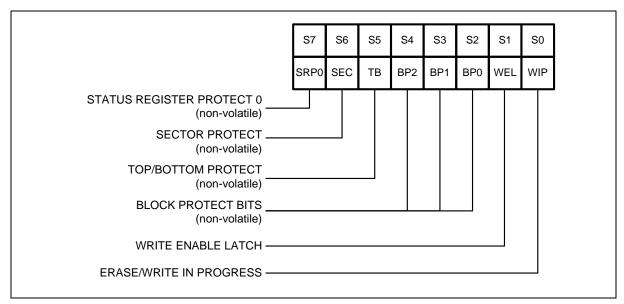

Figure 5 Status Register-1

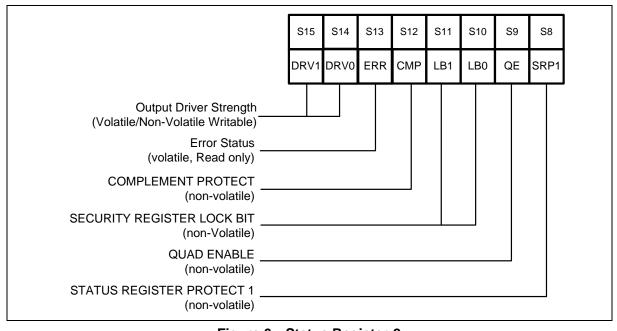

Figure 6 Status Register-2

### 10.1. WIP Bit

WIP is a read only bit in the status register (S0) that is set to a 1 state when the device is executing a Page Program, Quad Page Program, Sector Erase, Block Erase, Chip Erase, Write Status Register or Erase/Program Security Sector instruction. During this time the device will ignore further instructions except for the Read Status Register instruction (see  $t_W$ ,  $t_{PP}$ ,  $t_{SE}$ ,  $t_{BE}$ , and  $t_{CE}$  in "12.6 AC Electrical Characteristics"). When the program, erase or write status register (or security sector) instruction has completed, the WIP bit will be cleared to a 0 state indicating the device is ready for further instructions.

### 10.2. Write Enable Latch (WEL)

Write Enable Latch (WEL) is a read only bit in the status register (S1) that is set to 1 after executing a Write Enable Instruction. The WEL status bit is cleared to 0 when the device is write disabled. A write disable state occurs upon power-up or after any of the following instructions: Write Disable, Page Program, Quad Page Program, Sector Erase, Block Erase, Chip Erase, Write Status Register, Erase Security Sector and Program Security Sector.

## 10.3. Block Protect Bits (BP2, BP1, BP0)

The Block Protect Bits (BP2, BP1, BP0) are non-volatile read/write bits in the status register (S4, S3, and S2) that provide Write Protection control and status. Block Protect bits can be set using the Write Status Register Instruction (see  $t_W$  in "12.6 AC Electrical Characteristics"). All, none or a portion of the memory array can be protected from Program and Erase instructions (see Table 3 Status Register Memory Protection). The factory default setting for the Block Protection Bits is 0, none of the array protected.

# 10.4. Top/Bottom Block Protect (TB)

The non-volatile Top/Bottom bit (TB) controls if the Block Protect Bits (BP2, BP1, BP0) protect from the Top (TB=0) or the Bottom (TB=1) of the array as shown in Table 3 Status Register Memory Protection table. The factory default setting is TB=0. The TB bit can be set with the Write Status Register Instruction depending on the state of the SRP0, SRP1 and WEL bits.

# 10.5. Sector/Block Protect (SEC)

The non-volatile Sector/Block Protect bit (SEC) controls if the Block Protect Bits (BP2, BP1, BP0) protect either 4KB Sectors (SEC=1) or 64KB Blocks (SEC=0) in the Top (TB=0) or the Bottom (TB=1) of the array as shown in Table 3 Status Register Memory Protection table. The default setting is SEC=0.

# 10.6. Complement Protect (CMP)

The Complement Protect bit (CMP) is a non-volatile read/write bit in the status register (S14). It is used in conjunction with SEC, TB, BP2, BP1 and BP0 bits to provide more flexibility for the array protection. Once CMP is set to 1, previous array protection set by SEC, TB, BP2, BP1 and BP0 will be reversed. For instance, when CMP=0, a top 4KB sector can be protected while the rest of the array is not; when CMP=1, the top 4KB sector will become unprotected while the rest of the array become read-only. Please refer to Table 3 Status Register Memory Protection table for details. The default setting is CMP=0.

## 10.7. Status Register Protect (SRP1, SRP0)

The Status Register Protect bits (SRP1 and SRP0) are non-volatile read/write bits in the status register (S8 and S7). The SRP bits control the method of write protection: software protection, hardware protection, power supply lock-down or one time programmable (OTP) protection.

|      |      |     | 14510 2                   | Clarac Regions Fredoric Site                                                                                             |

|------|------|-----|---------------------------|--------------------------------------------------------------------------------------------------------------------------|

| SRP1 | SRP0 | WP# | Status<br>Register        | Description                                                                                                              |

| 0    | 0    | Х   | Software<br>Protection    | WP# pin has no control. The Status register can be written to after a Write Enable instruction, WEL=1. (Factory Default) |

| 0    | 1    | 0   | Hardware<br>Protected     | When WP# pin is low the Status Register locked and can not be written to.                                                |

| 0    | 1    | 1   | Hardware<br>Unprotected   | When WP# pin is high the Status register is unlocked and can be written to after a Write Enable instruction, WEL=1.      |

| 1    | 0    | Х   | Power Supply<br>Lock-Down | Status Register is protected and can not be written to again until the next power-down, power-up cycle. (1)              |

| 1    | 1    | Х   | One Time<br>Program       | Status Register is permanently protected and can not be written to                                                       |

Table 2 Status Register Protect bits

#### Note:

# 10.8. Error Bit (ERR)

The Error bit is a status flag, which shows the status of last Program/Erase operation. It will be set to "1", if the Program/Erase operation fails. It will be set to "0", after reset or WREN instruction.

## 10.9. Security Sector Lock Bits (LB1,LB0)

The Security Register Lock Bit (LB1-0) are non-volatile One Time Program (OTP) bits in Status Register (S12,S11) that provide the write protect control and status to the Security Registers. The default state of LB1-0 is 0, Security Registers are unlocked. LB1-0 can be set to 1 individually using the Write Status Register instruction. LB1-0 are One Time Programmable (OTP), once it's set to 1, the corresponding 512-Bytes Security Register will become read-only permanently.

# 10.10. Quad Enable (QE)

The Quad Enable (QE) bit is a non-volatile read/write bit in the status register (S9) that allows Quad SPI and QPI operation. When the QE bit is set to a 0 state (factory default), the WP# pin and HOLD# are enabled. When the QE bit is set to a 1, the Quad  $DQ_2$  and  $DQ_3$  pins are enabled, and WP# and HOLD# functions are disabled.

QE bit is required to be set to a 1 before issuing an "Enable QPI (38h)" to switch the device from Standard/Dual/Quad SPI to QPI, otherwise the command will be ignored. When the device is in QPI mode, QE bit will remain to be 1. A "Write Status Register" command in QPI mode cannot change QE bit from a "1" to a "0".

WARNING: If the WP# or HOLD# pins are tied directly to the power supply or ground during standard SPI or Dual SPI operation, the QE bit should never be set to a 1.

<sup>1.</sup> When SRP1, SRP0 = (1, 0), a power-down, power-up cycle will change SRP1, SRP0 to (0, 0) state.

# 10.11. Output driver strength (DRV1, DRV0)

The DRV1 & DRV0 bits are used to determine the output driver strength.

| ı               |

|-----------------|

| Driver Strength |

| 100%            |

| 75%             |

| 50%             |

| 25%             |

|                 |

# 10.12. Status Register Memory Protection

**Table 3** Status Register Memory Protection

|     | STA | TUS F | REGIS | TER |     | FM25Q08A (8M-BIT) MEMORY PROTECTION |                      |                   |                   |  |  |

|-----|-----|-------|-------|-----|-----|-------------------------------------|----------------------|-------------------|-------------------|--|--|

| СМР | SEC | ТВ    | BP2   | BP1 | BP0 | PROTECTED BLOCK(S)                  | PROTECTED ADDRESSES  | PROTECTED DENSITY | PROTECTED PORTION |  |  |

| 0   | Х   | Х     | 0     | 0   | 0   | NONE                                | NONE                 | NONE              | NONE              |  |  |

| 0   | 0   | 0     | 0     | 0   | 1   | 15                                  | 0F0000h –<br>0FFFFFh | 64KB              | Upper 1/16        |  |  |

| 0   | 0   | 0     | 0     | 1   | 0   | 14 and 15                           | 0E0000h –<br>0FFFFFh | 128KB             | Upper 1/8         |  |  |

| 0   | 0   | 0     | 0     | 1   | 1   | 12 thru 15                          | 0C0000h –<br>0FFFFFh | 256KB             | Upper 1/4         |  |  |

| 0   | 0   | 0     | 1     | 0   | 0   | 8 thru 15                           | 080000h –<br>0FFFFFh | 512KB             | Upper 1/2         |  |  |

| 0   | 0   | 1     | 0     | 0   | 1   | 0                                   | 000000h –<br>00FFFFh | 64KB              | Lower 1/16        |  |  |

| 0   | 0   | 1     | 0     | 1   | 0   | 0 and 1                             | 000000h –<br>01FFFFh | 128KB             | Lower 1/8         |  |  |

| 0   | 0   | 1     | 0     | 1   | 1   | 0 thru 3                            | 000000h –<br>03FFFFh | 256KB             | Lower 1/4         |  |  |

| 0   | 0   | 1     | 1     | 0   | 0   | 0 thru 7                            | 000000h –<br>07FFFFh | 512KB             | Lower 1/2         |  |  |

| 0   | 0   | Х     | 1     | 0   | 1   | 0 thru 15                           | 000000h –<br>0FFFFFh | 1MB               | ALL               |  |  |

| 0   | Х   | Х     | 1     | 1   | Х   | 0 thru 15                           | 000000h –<br>0FFFFFh | 1MB               | ALL               |  |  |

| 0   | 1   | 0     | 0     | 0   | 1   | 15                                  | 0FF000h –<br>0FFFFFh | 4KB               | U - 1/256         |  |  |

| 0   | 1   | 0     | 0     | 1   | 0   | 15                                  | 0FE000h –<br>0FFFFFh | 8KB               | U - 1/128         |  |  |

| 0   | 1   | 0     | 0     | 1   | 1   | 15                                  | 0FC000h –<br>0FFFFFh | 16KB              | U - 1/64          |  |  |

| 0   | 1   | 0     | 1     | 0   | Х   | 15                                  | 0F8000h –<br>0FFFFFh | 32KB              | U - 1/32          |  |  |

| 0   | 1   | 1     | 0     | 0   | 1   | 0                                   | 000000h –<br>000FFFh | 4KB               | L - 1/256         |  |  |

| 0   | 1   | 1     | 0     | 1   | 0   | 0                                   | 000000h –<br>001FFFh | 8KB               | L - 1/128         |  |  |

| 0   | 1   | 1     | 0     | 1   | 1   | 0                                   | 000000h –<br>003FFFh | 16KB              | L - 1/64          |  |  |

| 0   | 1   | 1     | 1     | 0   | Χ   | 0                                   | 000000h –<br>007FFFh | 32KB              | L - 1/32          |  |  |

| 1   | Х   | Χ     | 0     | 0   | 0   | 0 thru 15                           | 000000h –<br>0FFFFh  | ALL               | ALL               |  |  |

| 1   | 0   | 0     | 0     | 0   | 1   | 0 thru 14                           | 000000h –<br>0EFFFFh | 960KB             | Lower 15/16       |  |  |

| 1   | 0   | 0     | 0     | 1   | 0   | 0 and 13                            | 000000h –<br>0DFFFFh | 896KB             | Lower 7/8         |  |  |

| STATUS REGISTER FM25Q08A (8M-BIT) MEMORY PROTECTION |     |     |       |     |     |                    |                      |         |             |  |  |

|-----------------------------------------------------|-----|-----|-------|-----|-----|--------------------|----------------------|---------|-------------|--|--|

|                                                     | SIA | 105 | KEGIS | IEK | I   |                    |                      |         |             |  |  |

| CMP                                                 | SEC | ТВ  | BP2   | BP1 | BP0 | PROTECTED BLOCK(S) | ADDRESSES            | DENSITY | PORTION     |  |  |

| 1                                                   | 0   | 0   | 0     | 1   | 1   | 0 thru 11          | 000000h –<br>0BFFFFh | 768KB   | Lower 3/4   |  |  |

| 1                                                   | 0   | 0   | 1     | 0   | 0   | 0 thru 7           | 000000h –<br>07FFFFh | 512KB   | Lower 1/2   |  |  |

| 1                                                   | 0   | 1   | 0     | 0   | 1   | 1 thru 15          | 010000h –<br>0FFFFFh | 960KB   | Upper 15/16 |  |  |

| 1                                                   | 0   | 1   | 0     | 1   | 0   | 2 and 15           | 020000h –<br>0FFFFh  | 896KB   | Upper 7/8   |  |  |

| 1                                                   | 0   | 1   | 0     | 1   | 1   | 4 thru 15          | 040000h –<br>0FFFFFh | 768KB   | Upper 3/4   |  |  |

| 1                                                   | 0   | 1   | 1     | 0   | 0   | 8 thru 15          | 080000h –<br>0FFFFFh | 512KB   | Upper 1/2   |  |  |

| 1                                                   | 0   | Χ   | 1     | 0   | 1   | NONE               | NONE                 | NONE    | NONE        |  |  |

| 1                                                   | Χ   | Х   | 1     | 1   | Х   | NONE               | NONE                 | NONE    | NONE        |  |  |

| 1                                                   | 1   | 0   | 0     | 0   | 1   | 0 thru 15          | 000000h –<br>0FEFFFh | 1,020KB | L - 255/256 |  |  |

| 1                                                   | 1   | 0   | 0     | 1   | 0   | 0 thru 15          | 000000h –<br>0FDFFFh | 1,016KB | L - 127/128 |  |  |

| 1                                                   | 1   | 0   | 0     | 1   | 1   | 0 thru 15          | 000000h –<br>0FBFFFh | 1,008KB | L - 63/64   |  |  |

| 1                                                   | 1   | 0   | 1     | 0   | Х   | 0 thru 15          | 000000h –<br>0F7FFFh | 992KB   | L - 31/32   |  |  |

| 1                                                   | 1   | 1   | 0     | 0   | 1   | 0 thru 15          | 001000h –<br>0FFFFFh | 1,020KB | U - 255/256 |  |  |

| 1                                                   | 1   | 1   | 0     | 1   | 0   | 0 thru 15          | 002000h –<br>0FFFFFh | 1,016KB | U - 127/128 |  |  |

| 1                                                   | 1   | 1   | 0     | 1   | 1   | 0 thru 15          | 004000h –<br>0FFFFFh | 1,008KB | U - 63/64   |  |  |

| 1                                                   | 1   | 1   | 1     | 0   | Х   | 0 thru 15          | 008000h –<br>0FFFFFh | 992KB   | U - 31/32   |  |  |

# 11. Instructions

The Standard/Dual/Quad SPI instruction set of the FM25Q08A consists of 34 basic instructions that are fully controlled through the SPI bus (see Table 5~Table 7 Instruction Set). Instructions are initiated with the falling edge of Chip Select (CS#). The first byte of data clocked into the DI input provides the instruction code. Data on the DI input is sampled on the rising edge of clock with most significant bit (MSB) first.

The QPI instruction set of the FM25Q08A consists of 23 basic instructions that are fully controlled through the SPI bus (see Table 8 Instruction Set). Instructions are initiated with the falling edge of Chip Select (CS#). The first byte of data clocked through DQ[3:0] pins provides the instruction code. Data on all four DQ pins are sampled on the rising edge of clock with most significant bit (MSB) first. All QPI instructions, addresses, data and dummy bytes are using all four DQ pins to transfer every byte of data with every two serial clocks (CLK).

Instructions vary in length from a single byte to several bytes and may be followed by address bytes, data bytes, dummy bytes (don't care), and in some cases, a combination. Instructions are completed with the rising edge of edge CS#. Clock relative timing diagrams for each instruction are included in Figure 7 through Figure 68. All read instructions can be completed after any clocked bit. However, all instructions that Write, Program or Erase must complete on a byte boundary (CS# driven high after a full 8-bits have been clocked) otherwise the instruction will be ignored. This feature further protects the device from inadvertent writes. Additionally, while the memory is being programmed or erased, or when the Status Register is being written, all instructions except for Read Status Register will be ignored until the program or erase cycle has completed.

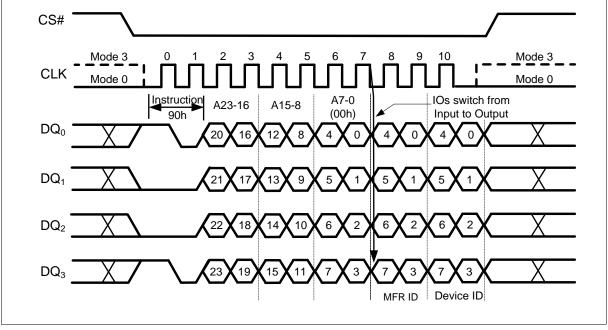

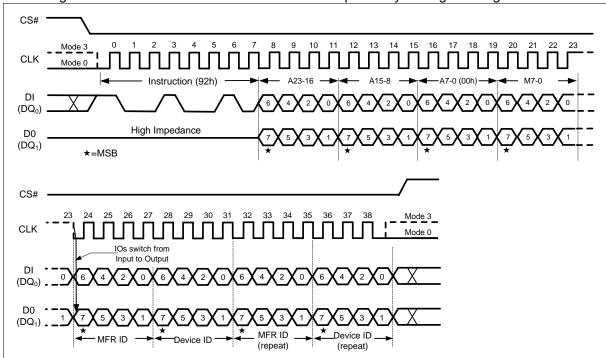

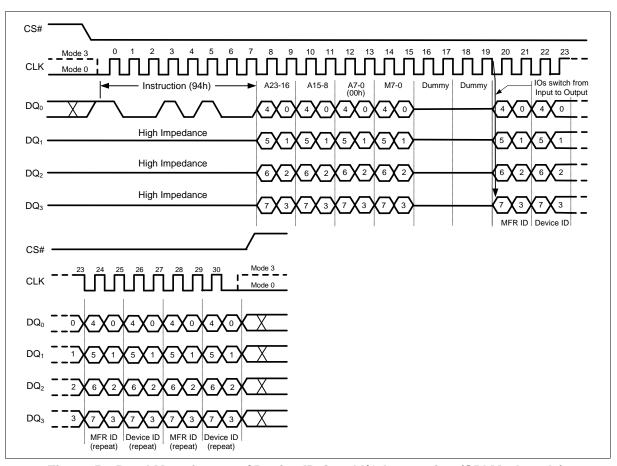

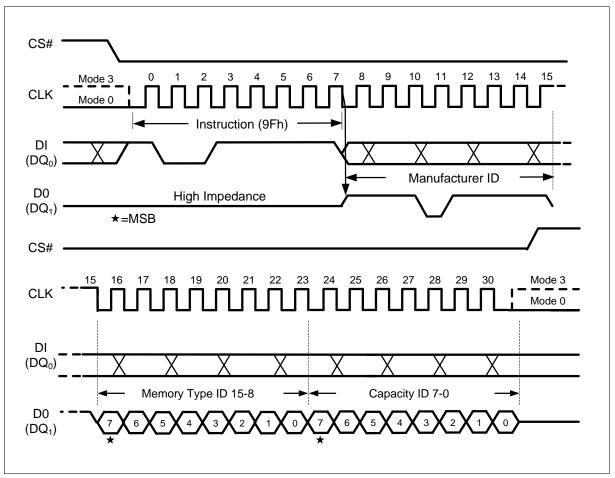

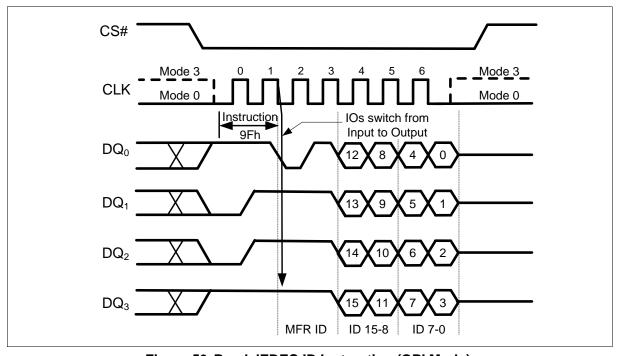

### 11.1. Manufacturer and Device Identification

Table 4 Manufacturer and Device Identification

| OP Code       | MF7-MF0 | ID15-ID0 | ID7-ID0 |

|---------------|---------|----------|---------|

| ABh           |         |          | 13h     |

| 90h, 92h, 94h | A1h     |          | 13h     |

| 9Fh           | A1h     | 4014h    |         |

# 11.2. Standard SPI Instructions Set

Table 5 Standard SPI Instructions Set (1)

| INSTRUCTION NAME                           | BYTE 1  | BYTE 2                        | BYTE 3                       | BYTE 4                | BYTE 5                   | BYTE 6               |

|--------------------------------------------|---------|-------------------------------|------------------------------|-----------------------|--------------------------|----------------------|

| CLOCK NUMBER                               | (0-7)   | (8-15)                        | (16-23)                      | (24-31)               | (32-39)                  | (40-47)              |

| Write Enable                               | 06h     |                               |                              |                       |                          |                      |

| Volatile SR Write Enable                   | 50h     |                               |                              |                       |                          |                      |

| Write Disable                              | 04h     |                               |                              |                       |                          |                      |

| Read Status Register-1                     | 05h     | (S7-S0) <sup>(2)</sup>        |                              |                       |                          |                      |

| Write Status Register-1                    | 01h     | S7-S0                         |                              |                       |                          |                      |

| Read Status Register-2                     | 35h     | (S15-S8) <sup>(2)</sup>       | 01h can b                    |                       | orogram Stati<br>1&2     | us Register-         |

| Write Status Register-2                    | 31h     | S15-S8                        |                              |                       |                          |                      |

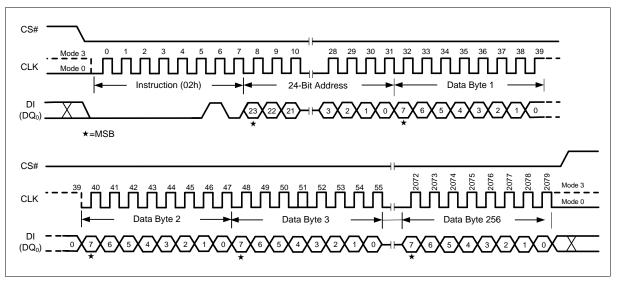

| Page Program                               | 02h     | A23-A16                       | A15-A8                       | A7-A0                 | D7-D0                    | D7-D0 <sup>(3)</sup> |

| Sector Erase (4KB)                         | 20h     | A23-A16                       | A15-A8                       | A7-A0                 |                          |                      |

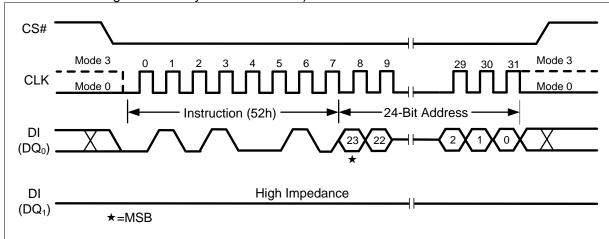

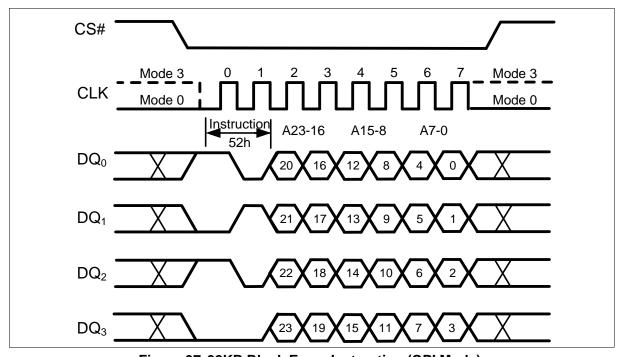

| Block Erase (32KB)                         | 52h     | A23-A16                       | A15-A8                       | A7-A0                 |                          |                      |

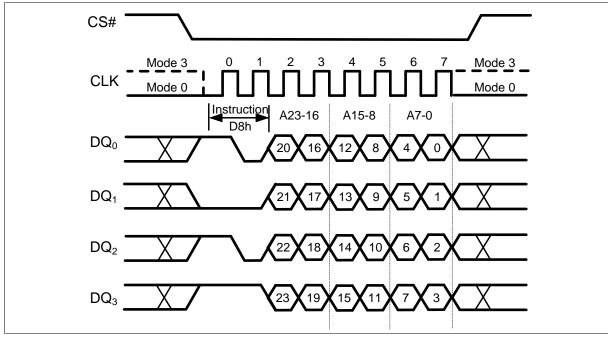

| Block Erase (64KB)                         | D8h     | A23-A16                       | A15-A8                       | A7-A0                 |                          |                      |

| Chip Erase                                 | C7h/60h |                               |                              |                       |                          |                      |

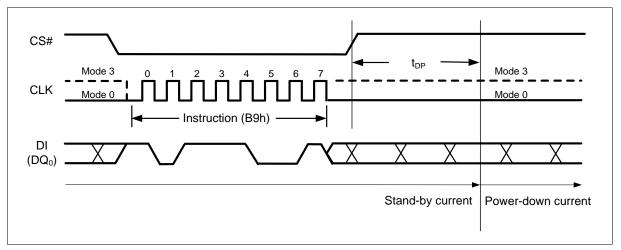

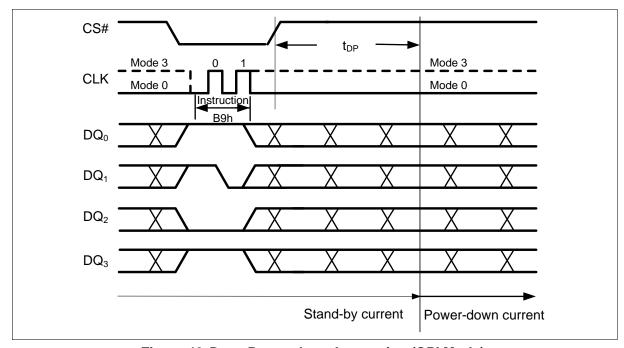

| Power-down                                 | B9h     |                               |                              |                       |                          |                      |

| Read Data                                  | 03h     | A23-A16                       | A15-A8                       | A7-A0                 | (D7-D0)                  |                      |

| Fast Read                                  | 0Bh     | A23-A16                       | A15-A8                       | A7-A0                 | dummy                    | (D7-D0)              |

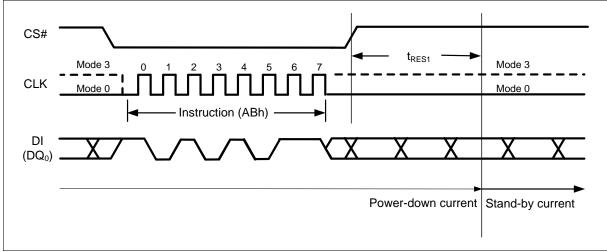

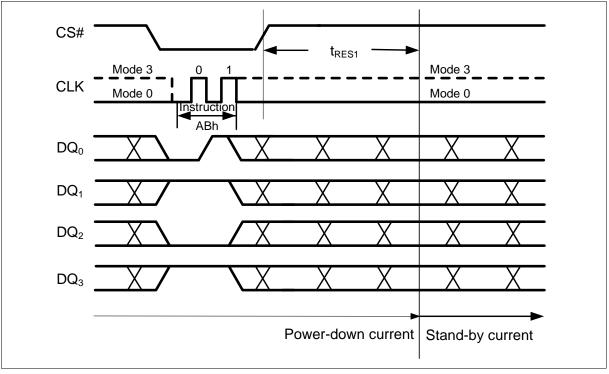

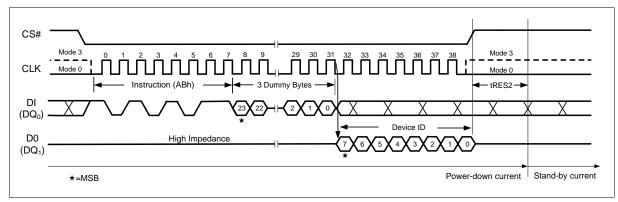

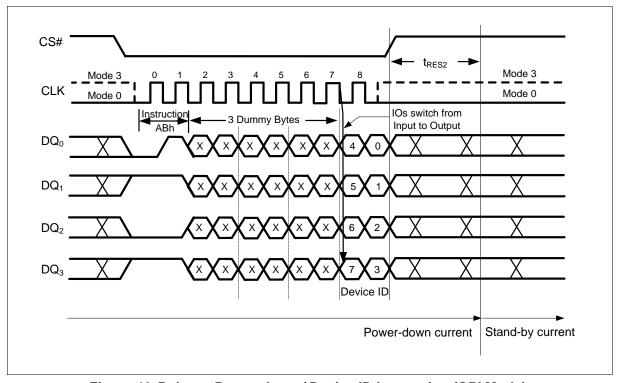

| Release Powerdown / ID <sup>(4)</sup>      | ABh     | dummy                         | dummy                        | dummy                 | (ID7-ID0) <sup>(2)</sup> |                      |

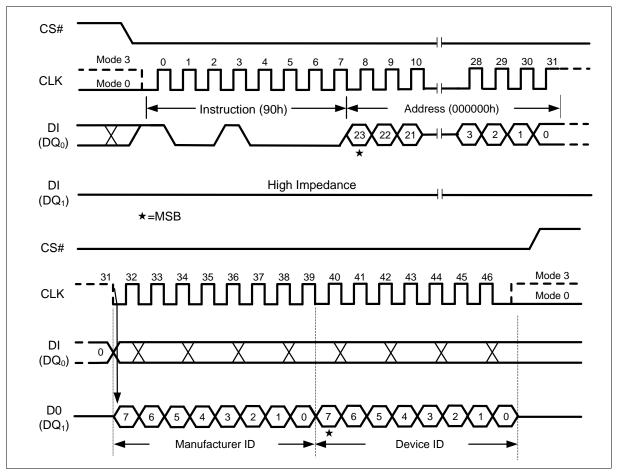

| Manufacturer/Device ID <sup>(4)</sup>      | 90h     | dummy                         | dummy                        | 00h                   | (MF7-MF0)                | (ID7-ID0)            |

| JEDEC ID <sup>(4)</sup>                    | 9Fh     | (MF7-MF0)<br>Manufactur<br>er | (ID15-ID8)<br>Memory<br>Type | (ID7-ID0)<br>Capacity |                          |                      |

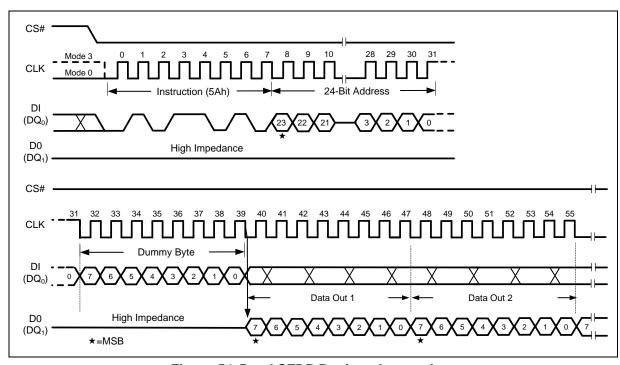

| Read SFDP Register                         | 5Ah     | 00h                           | 00h                          | A7-A0                 | dummy                    | (D7-D0)              |

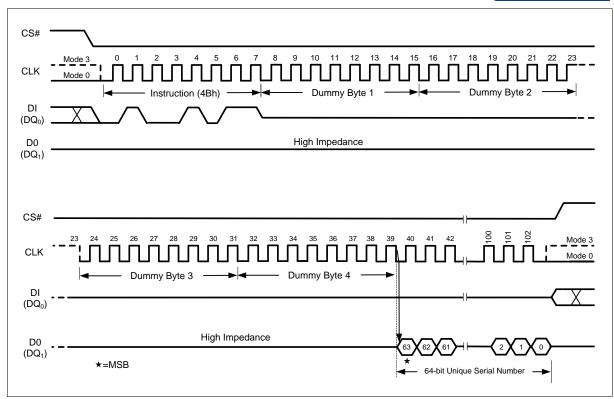

| Read Unique ID <sup>(5)</sup>              | 4Bh     | dummy                         | dummy                        | dummy                 | dummy                    | (UID63-<br>UID0)     |

| Erase Security Sectors <sup>(6)</sup>      | 44h     | A23-A16                       | A15-A8                       | A7-A0                 |                          |                      |

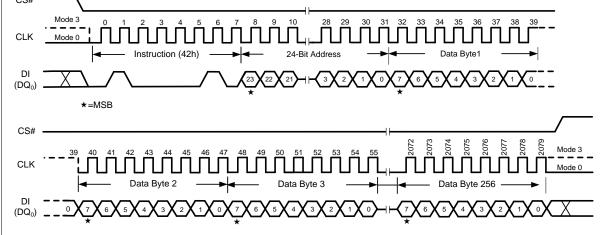

| Program Security<br>Sectors <sup>(6)</sup> | 42h     | A23-A16                       | A15-A8                       | A7-A0                 | D7-D0                    | D7-D0 <sup>(3)</sup> |

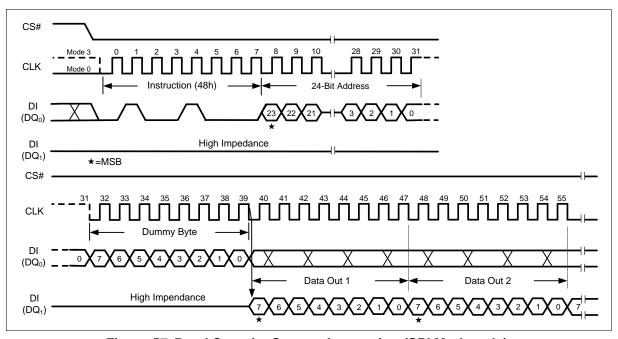

| Read Security Sectors <sup>(6)</sup>       | 48h     | A23-A16                       | A15-A8                       | A7-A0                 | dummy                    | (D7-D0)              |

| Enable QPI                                 | 38h     |                               |                              |                       |                          |                      |

| Enable Reset                               | 66h     |                               |                              |                       |                          |                      |

| Reset                                      | 99h     |                               |                              |                       |                          |                      |

# 11.3. Dual SPI Instructions Set

Table 6 Dual SPI Instructions Set

| INSTRUCTION NAME                                        | BYTE 1 | BYTE 2                | BYTE 3                          | BYTE 4                      | BYTE 5  | BYTE 6                  |

|---------------------------------------------------------|--------|-----------------------|---------------------------------|-----------------------------|---------|-------------------------|

| CLOCK NUMBER                                            | (0-7)  | (8-15)                | (16-23)                         | (24-31)                     | (32-39) | (40-47)                 |

| Fast Read Dual<br>Output                                | 3Bh    | A23-A16               | A15-A8                          | A7-A0                       | dummy   | (D7-D0,) <sup>(8)</sup> |

| Fast Read Dual I/O                                      | BBh    | A23-A8 <sup>(7)</sup> | A7-A0, M7-<br>M0 <sup>(7)</sup> | (D7-<br>D0,) <sup>(8)</sup> |         |                         |

| Manufacturer/Device<br>ID by<br>Dual I/O <sup>(4)</sup> | 92h    | A23-A8 <sup>(7)</sup> | A7-A0, M7-<br>M0 <sup>(7)</sup> | (MF7-MF0,<br>ID7-ID0)       |         |                         |

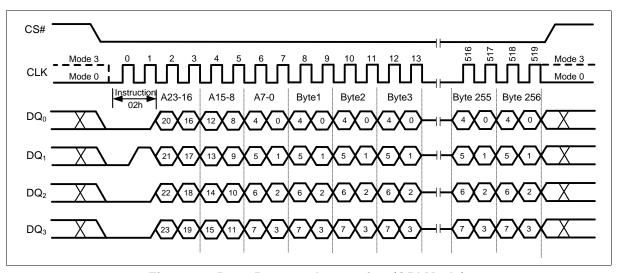

### 11.4. Quad SPI Instructions Set

Table 7 Quad SPI Instructions Set

| INSTRUCTION NAME                                       | BYTE 1 | BYTE 2                          | BYTE 3                            | BYTE 4                       | BYTE 5                     | BYTE 6                   |

|--------------------------------------------------------|--------|---------------------------------|-----------------------------------|------------------------------|----------------------------|--------------------------|

| CLOCK NUMBER                                           | (0-7)  | (8-15)                          | (16-23)                           | (24-31)                      | (32-39)                    | (40-47)                  |

| Quad Page Program                                      | 32h    | A23-A16                         | A15-A8                            | A7-A0                        | D7-<br>D0, <sup>(10)</sup> | D7-D0, <sup>(3)</sup>    |

| Fast Read Quad<br>Output                               | 6Bh    | A23-A16                         | A15-A8                            | A7-A0                        | dummy                      | (D7-D0,) <sup>(10)</sup> |

| Fast Read Quad I/O                                     | EBh    | A23-A0,<br>M7-M0 <sup>(9)</sup> | (xxxx, D7-<br>D0) <sup>(11)</sup> | (D7-<br>D0,) <sup>(10)</sup> |                            |                          |

| Word Read Quad I/O <sup>(13)</sup>                     | E7h    | A23-A0,<br>M7-M0 <sup>(9)</sup> | (xx, D7-<br>D0) <sup>(12)</sup>   | (D7-<br>D0,) <sup>(10)</sup> |                            |                          |

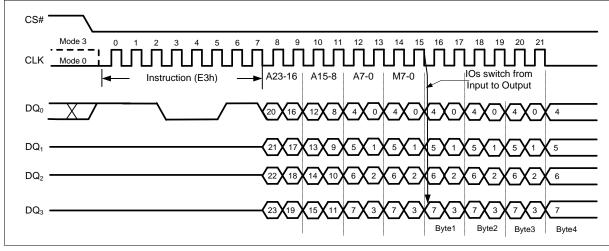

| Octal Word Read<br>Quad I/O <sup>(14)</sup>            | E3h    | A23-A0,<br>M7-M0 <sup>(9)</sup> | (D7-<br>D0,) <sup>(10)</sup>      |                              |                            |                          |

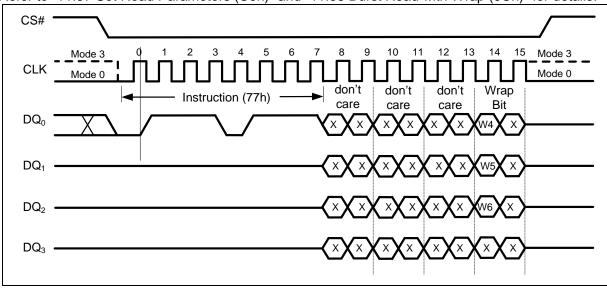

| Set Burst with Wrap                                    | 77h    | xxxxxx,<br>W6-W4 <sup>(9)</sup> |                                   |                              |                            |                          |

| Manufacture/Device<br>ID by<br>Quad I/O <sup>(4)</sup> | 94h    | A23-A0,<br>M7-M0 <sup>(9)</sup> | xxxx, (MF7-<br>MF0, ID7-<br>ID0)  | (MF7-MF0, ID7-ID0,)          |                            |                          |

# 11.5. QPI Instructions Set

Table 8 QPI Instructions Set (15)

| INSTRUCTION NAME            | BYTE 1 | BYTE 2                  | BYTE 3                                         | BYTE 4 | BYTE 5 | BYTE 6  |  |

|-----------------------------|--------|-------------------------|------------------------------------------------|--------|--------|---------|--|

| CLOCK NUMBER                | (0,1)  | (2,3)                   | (4,5)                                          | (6,7)  | (8,9)  | (10,11) |  |

| Write Enable                | 06h    |                         |                                                |        |        |         |  |

| Volatile SR Write<br>Enable | 50h    |                         |                                                |        |        |         |  |

| Write Disable               | 04h    |                         |                                                |        |        |         |  |

| Read Status Register-1      | 05h    | (S7-S0) <sup>(2)</sup>  |                                                |        |        |         |  |

| Write Status Register-1     | 01h    | S7-S0                   | 01h can be used to program Status Register 1&2 |        |        |         |  |

| Read Status Register-2      | 35h    | (S15-S8) <sup>(2)</sup> |                                                |        |        |         |  |

| Write Status Register-2     | 31h    | S18-S8                  |                                                |        |        |         |  |

| INSTRUCTION NAME                        | BYTE 1  | BYTE 2                        | BYTE 3                           | BYTE 4                    | BYTE 5                   | BYTE 6               |

|-----------------------------------------|---------|-------------------------------|----------------------------------|---------------------------|--------------------------|----------------------|

| Page Program                            | 02h     | A23-A16                       | A15-A8                           | A7-A0                     | D7-D0 <sup>(10)</sup>    | D7-D0 <sup>(3)</sup> |

| Sector Erase (4KB)                      | 20h     | A23-A16                       | A15-A8                           | A7-A0                     |                          |                      |

| Block Erase (32KB)                      | 52h     | A23-A16                       | A15-A8                           | A7-A0                     |                          |                      |

| Block Erase (64KB)                      | D8h     | A23-A16                       | A15-A8                           | A7-A0                     |                          |                      |

| Chip Erase                              | C7h/60h |                               |                                  |                           |                          |                      |

| Power-down                              | B9h     |                               |                                  |                           |                          |                      |

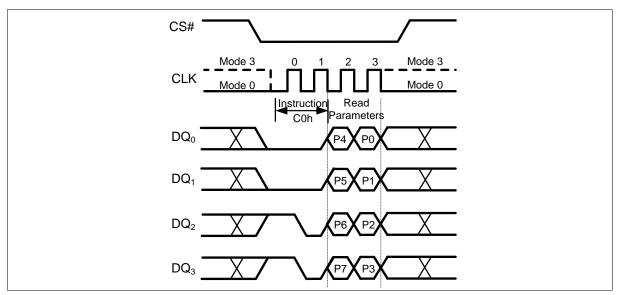

| Set Read Parameters                     | C0h     | P7-P0                         |                                  |                           |                          |                      |

| Fast Read                               | 0Bh     | A23-A16                       | A15-A8                           | A7-A0                     | dummy <sup>(16)</sup>    | (D7-D0)              |

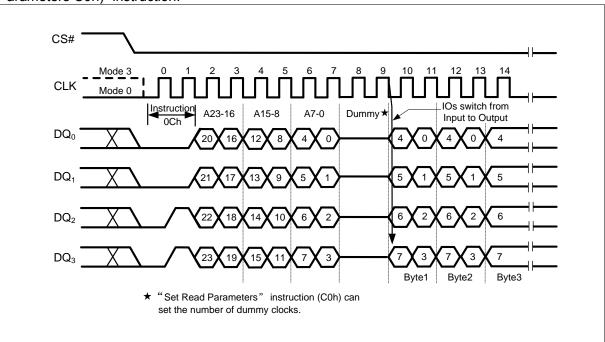

| Burst Read with<br>Wrap <sup>(17)</sup> | 0Ch     | A23-A16                       | A15-A8                           | A7-A0                     | dummy <sup>(16)</sup>    | (D7-D0)              |

| Fast Read Quad I/O                      | EBh     | A23-A16                       | A15-A8                           | A7-A0                     | M7-M0 <sup>(16)</sup>    | (D7-D0)              |

| Release Powerdown / ID <sup>(4)</sup>   | ABh     | dummy                         | dummy                            | dummy                     | (ID7-ID0) <sup>(2)</sup> |                      |

| Manufacturer/Device ID <sup>(4)</sup>   | 90h     | dummy                         | dummy                            | 00h                       | (MF7-MF0)                | (ID7-ID0)            |

| JEDEC ID(4)                             | 9Fh     | (MF7-MF0)<br>Manufactur<br>er | (ID15-<br>ID8)<br>Memory<br>Type | (ID7-<br>ID0)<br>Capacity |                          |                      |

| Disable QPI                             | FFh     |                               |                                  |                           |                          |                      |

| Enable Reset                            | 66h     |                               |                                  |                           |                          |                      |

| Reset                                   | 99h     |                               |                                  |                           |                          |                      |

#### Notes:

- 1. Data bytes are shifted with Most Significant Bit first. Byte fields with data in parenthesis "()" indicate data output from the device on either 1, 2 or 4 DQ pins.

- 2. The Status Register contents and Device ID will repeat continuously until CS# terminates the instruction.

- At least one byte of data input is required for Page Program, Quad Page Program and Program Security Sectors, up to 256 bytes of data input. If more than 256 bytes of data are sent to the device, the addressing will wrap to the beginning of the page and overwrite previously sent data.

- 4. See Table 4 Manufacturer and Device Identification table for device ID information.

- 5. This feature is available upon special order. Please contact Shanghai Fudan Microelectronics Group Co., Ltd for details.

Set Burst with Wrap input format:

$DQ_0 = x, x, x, x, x, x, W4, x$

$DQ_1 = x, x, x, x, x, x, W5, x$

$DQ_2 = x, x, x, x, x, x, W6, x$

$DQ_3 = x, x, x, x, x, x, x, x$

- 6. Security Sector Address:

- Security Sector 1: A23-A12 = 000h; A11-A8=00~01h; A7-A0 = byte address Security Sector 2: A23-A12 = 001h; A11-A8=00~01h; A7-A0 = byte address

- 7. Dual SPI address input format:

- $DQ_0 = A22$ , A20, A18, A16, A14, A12, A10, A8 A6, A4, A2, A0, M6, M4, M2, M0  $DQ_1 = A23$ , A21, A19, A17, A15, A13, A11, A9 A7, A5, A3, A1, M7, M5, M3, M1

- 8. Dual SPI data output format:

- $DQ_0 = (D6, D4, D2, D0)$

- $DQ_1 = (D7, D5, D3, D1)$

- 9. Quad SPI address input format:

- $DQ_0 = A20$ , A16, A12, A8, A4, A0, M4, M0

- $DQ_1 = A21, A17, A13, A9, A5, A1, M5, M1$

- $DQ_2 = A22$ , A18, A14, A10, A6, A2, M6, M2

- $DQ_3 = A23$ , A19, A15, A11, A7, A3, M7, M3

- 10. Quad SPI data input/output format:

- $DQ_0 = (D4, D0, ...)$

- $DQ_1 = (D5, D1, ....)$

- $DQ_2 = (D6, D2, ....)$

- $DQ_3 = (D7, D3, ....)$

Shanghai Fudan Microelectronics Group Company Limited =

11. Fast Read Quad I/O data output format:

```

DQ_0 = (x, x, x, x, D4, D0, D4, D0)

```

$$DQ_1 = (x, x, x, x, D5, D1, D5, D1)$$

$$DQ_2 = (x, x, x, x, D6, D2, D6, D2)$$

$$DQ_3 = (x, x, x, x, D7, D3, D7, D3)$$

12. Word Read Quad I/O data output format:

$$DQ_0 = (x, x, D4, D0, D4, D0, D4, D0)$$

$$DQ_1 = (x, x, D5, D1, D5, D1, D5, D1)$$

$$DQ_2 = (x, x, D6, D2, D6, D2, D6, D2)$$

$$DQ_3 = (x, x, D7, D3, D7, D3, D7, D3)$$

- 13. For Word Read Quad I/O, the lowest address bit must be 0. (A0 = 0)

- 14. For Octal Word Read Quad I/O, the lowest four address bits must be 0. (A3, A2, A1, A0 = 0)

- 15. QPI Command Address, Data input/output format:

| CLK#   | 0  | 1  | 2   | 3   | 4   | 5   | 6  | 7  | 8  | 9  | 10 | 11 |

|--------|----|----|-----|-----|-----|-----|----|----|----|----|----|----|

| $DQ_0$ | C4 | C0 | A20 | A16 | A12 | A8  | A4 | A0 | D4 | D0 | D4 | D0 |

| $DQ_1$ | C5 | C1 | A21 | A17 | A13 | A9  | A5 | A1 | D5 | D1 | D5 | D1 |

| $DQ_2$ | C6 | C2 | A22 | A18 | A14 | A10 | A6 | A2 | D6 | D2 | D6 | D2 |

| $DQ_3$ | C7 | C3 | A23 | A19 | A15 | A11 | A7 | А3 | D7 | D3 | D7 | D3 |

- 16. The number of dummy clocks for QPI Fast Read, QPI Fast Read Quad I/O & QPI Burst Read with Wrap is controlled by read parameter P7 ~ P4.

- 17. The wrap around length for QPI Burst Read with Wrap is controlled by read parameter P3 ~ P0.

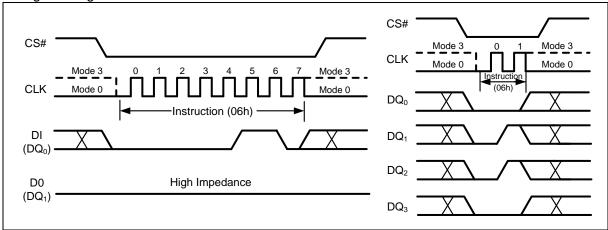

## 11.6. Write Enable (WREN) (06h)

The Write Enable (WREN) instruction (Figure 7) sets the Write Enable Latch (WEL) bit in the Status Register to a 1. The WEL bit must be set prior to every Page Program, Quad Page Program, Sector Erase, Block Erase, Chip Erase, Write Status Register and Erase/Program Security Sectors instruction. The Write Enable (WREN) instruction is entered by driving CS# low, shifting the instruction code "06h" into the Data Input (DI) pin on the rising edge of CLK, and then driving CS# high.

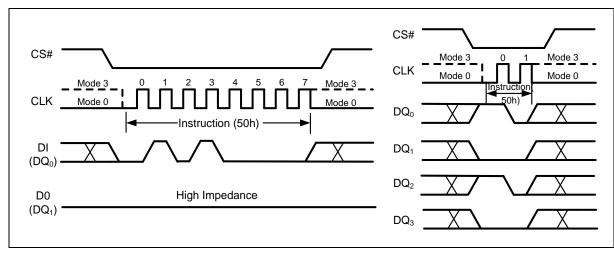

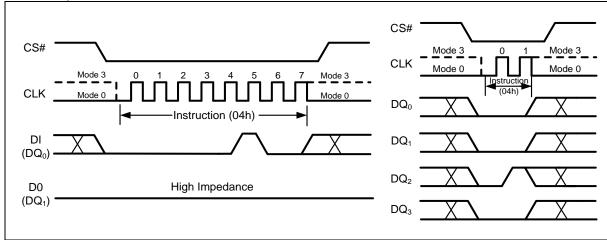

Figure 7 Write Enable Instruction for SPI Mode (left) or QPI Mode (right)

# 11.7. Write Enable for Volatile Status Register (50h)

The non-volatile Status Register bits described in section 10.1 can also be written to as volatile bits. This gives more flexibility to change the system configuration and memory protection schemes quickly without waiting for the typical non-volatile bit write cycles or affecting the endurance of the Status Register non-volatile bits. To write the volatile values into the Status Register bits, the Write Enable for Volatile Status Register (50h) instruction must be issued prior to a Write Status Register (01h/31h) instruction. Write Enable for Volatile Status Register instruction (Figure 8) will not set the Write Enable Latch (WEL) bit, it is only valid for the Write Status Register instruction to change the volatile Status Register bit values.

Figure 8 Write Enable for Volatile Status Register Instruction for SPI Mode (left) or QPI Mode (right)

## 11.8. Write Disable (WRDI) (04h)

The Write Disable (WRDI) instruction (Figure 9) resets the Write Enable Latch (WEL) bit in the Status Register to a 0. The Write Disable (WRDI) instruction is entered by driving CS# low, shifting the instruction code "04h" into the DI pin and then driving CS# high. Note that the WEL bit is automatically reset after Power-up and upon completion of the Write Status Register, Erase/Program Security Sectors, Page Program, Quad Page Program, Sector Erase, Block Erase, Chip Erase and Reset instructions.

Figure 9 Write Disable Instruction for SPI Mode (left) or QPI Mode (right)

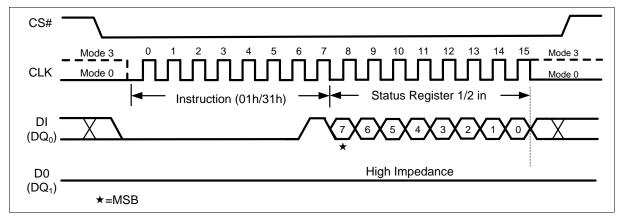

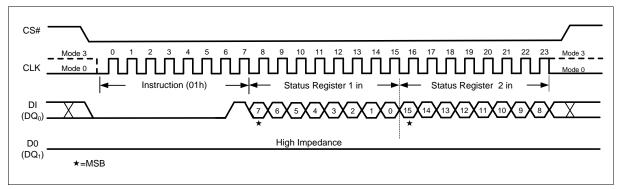

# 11.9. Read Status Register-1 (RDSR1) (05h), Status Register-2 (RDSR2) (35h)

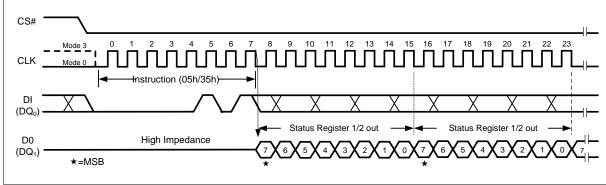

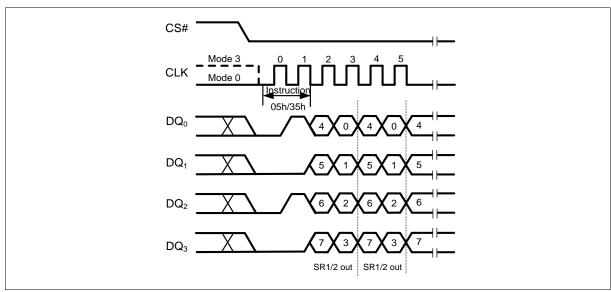

The Read Status Register instructions allow the 8-bit Status Registers to be read. The instruction is entered by driving CS# low and shifting the instruction code "05h" for Status Register-1 or "35h" for Status Register-2 into the DI pin on the rising edge of CLK. The status register bits are then shifted out on the DO pin at the falling edge of CLK with most significant bit (MSB) first as shown in Figure 10. The Status Register bits are shown in Figure 5 and Figure 6.

The Read Status Register instruction may be used at any time, even while a Program, Erase or Write Status Register cycle is in progress. This allows the WIP status bit to be checked to determine when the cycle is complete and if the device can accept another instruction. The Status Register can be read continuously, as shown in Figure 11. The instruction is completed by driving CS# high.

Figure 10 Read Status Register Instruction (SPI Mode)

Figure 11 Read Status Register Instruction (QPI Mode)

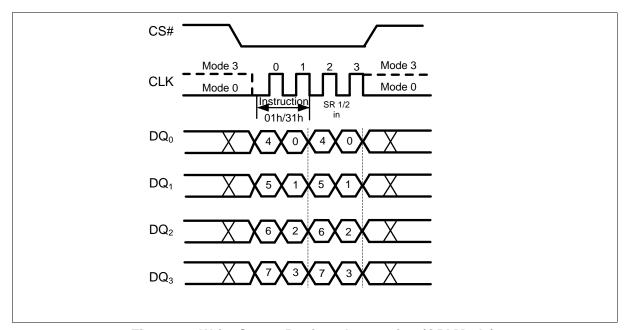

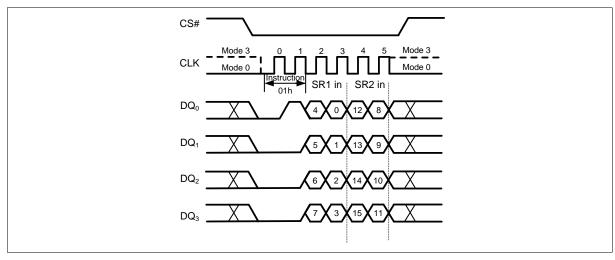

# 11.10. Write Status Register-1(WRSR) (01h), Status Register-2 (31h)

The Write Status Register (WRSR) instruction allows the Status Register to be written. Only non-volatile Status Register bits SRP0, SEC, TB, BP2, BP1, BP0 (bits 7 thru 2 of Status Register-1), DRV0, DRV1, CMP, LB1, LB0 QE, SRP1 (bits 15 thru 14 and 12 thru 8 of Status Register-2), can be written to. All other Status Register bit locations are read-only and will not be affected by the Write Status Register (WRSR) instruction. LB1-0 are non-volatile OTP bits, once it is set to 1, it cannot be cleared to 0. The Status Register bits are shown in shown in Figure 5 and Figure 6 and described in 10 Status Register.

To write non-volatile Status Register bits, a standard Write Enable (06h) instruction must previously have been executed for the device to accept the Write Status Register (WRSR) instruction (Status Register bit WEL must equal 1). Once write enabled, the instruction is entered by driving CS# low, sending the instruction code "01h", and then writing the status register data byte as illustrated in Figure 12 and Figure 13.

To write volatile Status Register bits, a Write Enable for Volatile Status Register (50h) instruction must have been executed prior to the Write Status Register (WRSR) instruction (Status Register bit WEL remains 0). However, SRP1 and LB1-0, cannot be changed from "1" to "0" because of the OTP protection for these bits. Upon power off or the execution of a "Reset (99h)" instruction, the volatile Status Register bit values will be lost, and the non-volatile Status Register bit values will be restored.

To complete the Write Status Register (WRSR) instruction, the CS# pin must be driven high after the eighth or sixteenth bit of data that is clocked in. If this is not done the Write Status Register (WRSR) instruction will not be executed.

During non-volatile Status Register write operation (06h combined with 01h), after CS# is driven high, the self-timed Write Status Register cycle will commence for a time duration of  $t_W$  (See "12.6 AC Electrical Characteristics"). While the Write Status Register cycle is in progress, the Read Status Register instruction may still be accessed to check the status of the WIP bit. The WIP bit is a 1 during the Write Status Register cycle and a 0 when the cycle is finished and ready to accept other instructions again. After the Write Status Register cycle has finished, the Write Enable Latch (WEL) bit in the Status Register will be cleared to 0.

During volatile Status Register write operation (50h combined with 01h), after CS# is driven high, the Status Register bits will be refreshed to the new values within the time period of t<sub>SHSL2</sub> (See "12.6 AC Electrical Characteristics"). WIP bit will remain 0 during the Status Register bit refresh period.

The Write Status Register (WRSR) instruction can be used in both SPI mode and QPI mode. However, the QE bit cannot be written to when the device is in the QPI mode, because QE=1 is required for the device to enter and operate in the QPI mode.

Figure 12 Write Status Register Instruction (SPI Mode)

Figure 13 Write Status Register Instruction (QPI Mode)

The FM25Q08A is also backward compatible to FMSH's previous generations of serial flash memories, in which the Status Register-1&2 can be written using a single "Write Register-1(01h)" command. To complete the Write Status Register1&2, the CS# pin must be driven high after the sixteenth bit of data that is clocked in as shown in Figure 14 & Figure 15 . If CS# is driven high after the eighth clock, the Write Status Register (WRSR) instruction will only program the Status Register-1, the Status Register-2 will not be affected.

Figure 14 Write Status Register-1/2 Instruction (backward compatible, SPI Mode)

Figure 15 Write Status Register-1/2 Instruction (backward compatible, QPI Mode)

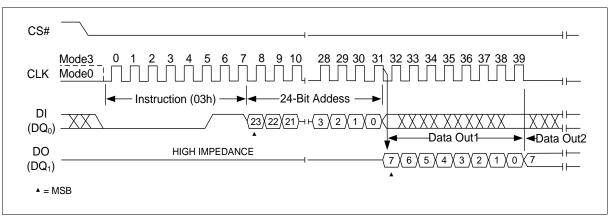

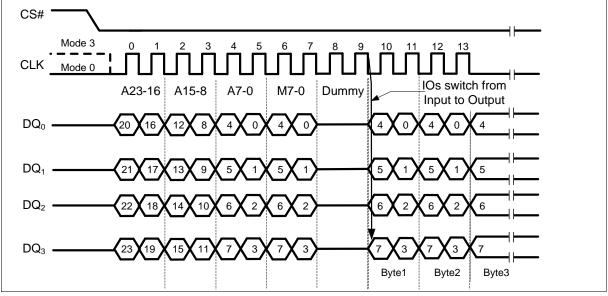

## 11.11. Read Data (03h)

The Read Data instruction allows one or more data bytes to be sequentially read from the memory. The instruction is initiated by driving the CS# pin low and then shifting the instruction code "03h" followed by a 24-bit address A23-A0 into the DI pin. The code and address bits are latched on the rising edge of the CLK pin. After the address is received, the data byte of the addressed memory location will be shifted out on the DO pin at the falling edge of CLK with most significant bit (MSB) first. The address is automatically incremented to the next higher address after each byte of data is shifted out allowing for a continuous stream of data. This means that the entire memory can be accessed with a single instruction as long as the clock continues. The instruction is completed by driving CS# high.

The Read Data instruction sequence is shown in Figure 16. If a Read Data instruction is issued while an Erase, Program or Write cycle is in process (WIP =1) the instruction is ignored and will not have any effect on the current cycle. The Read Data instruction allows clock rates from D.C. to a maximum of  $f_R$  (see "12.6 AC Electrical Characteristics").

The Read Data (03h) instruction is only supported in Standard SPI mode.

Figure 16 Read Data Instruction (SPI Mode only)

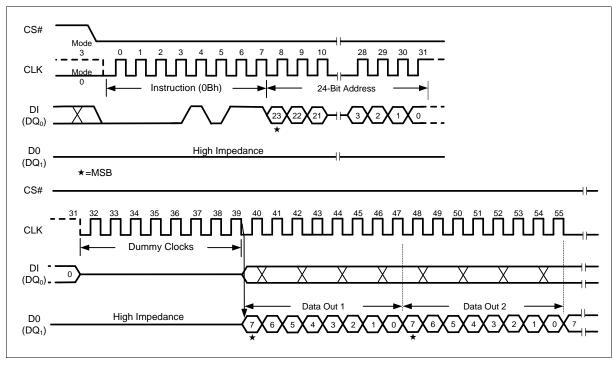

# 11.12. Fast Read (0Bh)

The Fast Read instruction is similar to the Read Data instruction except that it can operate at the highest possible frequency of  $F_R$  (see "12.6 AC Electrical Characteristics"). This is accomplished by adding eight "dummy" clocks after the 24-bit address as shown in Figure 17. The dummy clocks allow the devices internal circuits additional time for setting up the initial address. During the dummy clocks the data value on the DI pin is a "don't care".

Figure 17 Fast Read Instruction (SPI Mode)

### Fast Read (0Bh) in QPI Mode

The Fast Read instruction is also supported in QPI mode. When QPI mode is enabled, the number of dummy clocks is configured by the "Set Read Parameters (C0h)" instruction to accommodate wide range applications with different needs for either maximum Fast Read frequency or minimum data access latency. Depending on the Read Parameter Bits P[5:4] setting, the number of dummy clocks can be configured as either 2, 4, 6 or 8. The default number of dummy clocks upon power up or after a Reset instruction is 2.

Figure 18 Fast Read Instruction (QPI Mode)

# 11.13. Fast Read Dual Output (3Bh)

The Fast Read Dual Output (3Bh) instruction is similar to the standard Fast Read (0Bh) instruction except that data is output on two pins;  $DQ_0$  and  $DQ_1$ . This allows data to be transferred from the FM25Q08A at twice the rate of standard SPI devices. The Fast Read Dual Output instruction is ideal for quickly downloading code from Flash to RAM upon power-up or for applications that cache code-segments to RAM for execution.

Similar to the Fast Read instruction, the Fast Read Dual Output instruction can operate at the highest possible frequency of  $F_R$  (see "12.6 AC Electrical Characteristics"). This is accomplished by adding eight "dummy" clocks after the 24-bit address as shown in Figure 19. The dummy clocks allow the device's internal circuits additional time for setting up the initial address. The input data during the dummy clocks is "don't care". However, the  $DQ_0$  pin should be high-impedance prior to the falling edge of the first data out clock.

Figure 19 Fast Read Dual Output Instruction (SPI Mode only)

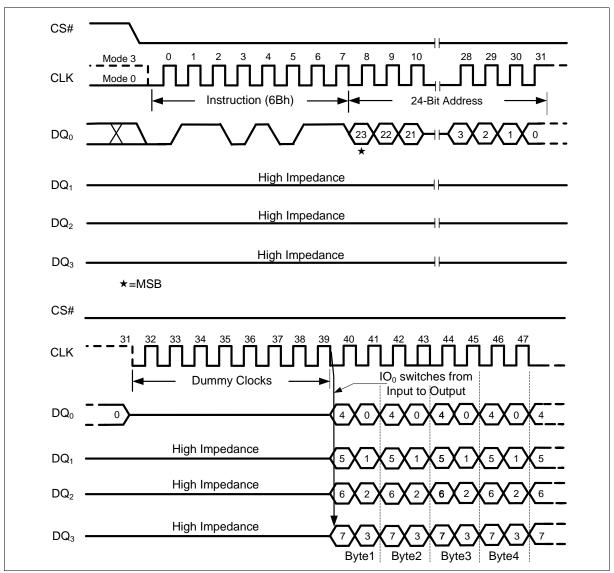

## 11.14. Fast Read Quad Output (6Bh)

The Fast Read Quad Output (6Bh) instruction is similar to the Fast Read Dual Output (3Bh) instruction except that data is output on four pins, DQ<sub>0</sub>, DQ<sub>1</sub>, DQ<sub>2</sub>, and DQ<sub>3</sub>. A Quad enable of Status Register-2 must be executed before the device will accept the Fast Read Quad Output Instruction (Status Register bit QE must equal 1). The Fast Read Quad Output Instruction allows data to be transferred from the FM25Q08A at four times the rate of standard SPI devices.

The Fast Read Quad Output instruction can operate at the highest possible frequency of  $F_R$  (see "12.6 AC Electrical Characteristics"). This is accomplished by adding eight "dummy" clocks after the 24-bit address as shown in Figure 20. The dummy clocks allow the device's internal circuits additional time for setting up the initial address. The input data during the dummy clocks is "don't care". However, the DQ pins should be high-impedance prior to the falling edge of the first data out clock.

Figure 20 Fast Read Quad Output Instruction (SPI Mode only)

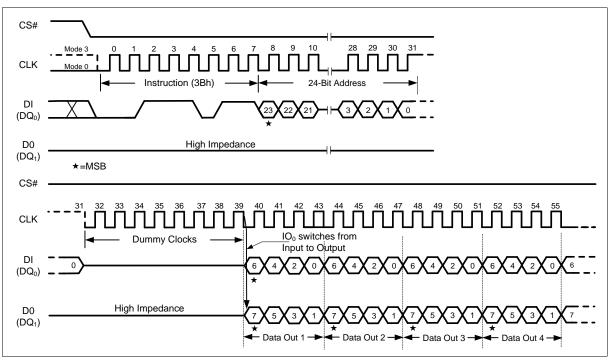

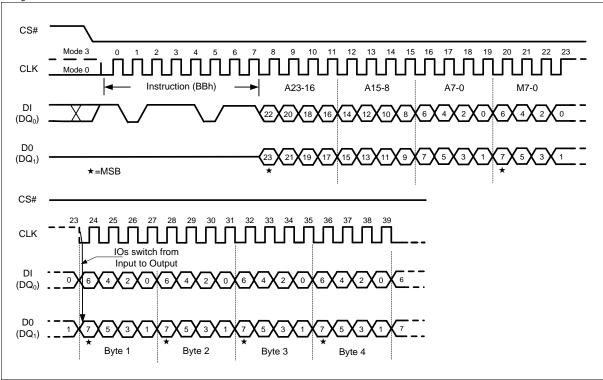

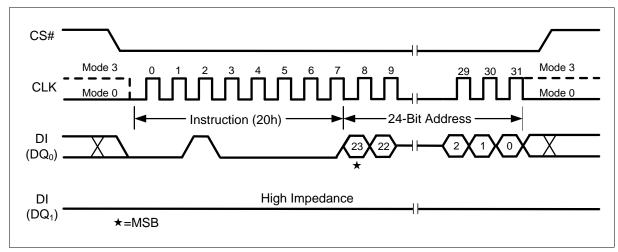

# 11.15. Fast Read Dual I/O (BBh)

The Fast Read Dual I/O (BBh) instruction allows for improved random access while maintaining two I/O pins,  $DQ_0$  and  $DQ_1$ . It is similar to the Fast Read Dual Output (3Bh) instruction but with the capability to input the Address bits A23-A0 two bits per clock. This reduced instruction overhead may allow for code execution (XIP) directly from the Dual SPI in some applications.

#### Fast Read Dual I/O with "Continuous Read Mode"

The Fast Read Dual I/O instruction can further reduce instruction overhead through setting the "Continuous Read Mode" bits (M7-0) after the input Address bits A23-A0, as shown in Figure 21. The upper nibble of the (M7-4) controls the length of the next Fast Read Dual I/O instruction through the inclusion or exclusion of the first byte instruction code. The lower nibble bits of the (M3-0) are don't care ("x"). However, the DQ pins should be high-impedance prior to the falling edge of the first data out clock.

If the "Continuous Read Mode" bits M5-4 = (1,0), then the next Fast Read Dual I/O instruction (after CS# is raised and then lowered) does not require the BBh instruction code, as shown in Figure 22. This reduces the instruction sequence by eight clocks and allows the Read address to

be immediately entered after CS# is asserted low. If the "Continuous Read Mode" bits M5-4 do not equal to (1,0), the next instruction (after CS# is raised and then lowered) requires the first byte instruction code, thus returning to normal operation. It is recommended to input FFFFh on  $DQ_0$  for the next

Figure 21 Fast Read Dual I/O Instruction (Initial instruction or previous M5-4 ≠ 10, SPI Mode only)

Figure 22 Fast Read Dual I/O Instruction (Previous instruction set M5-4 = 10, SPI Mode only)

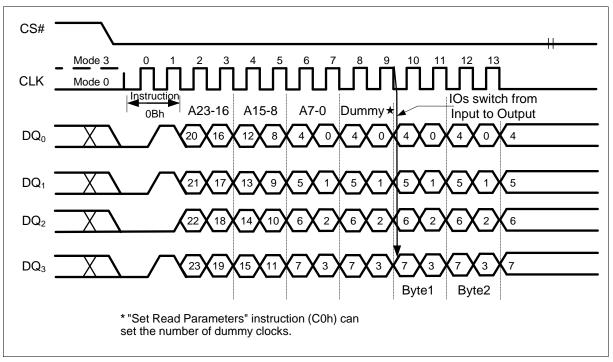

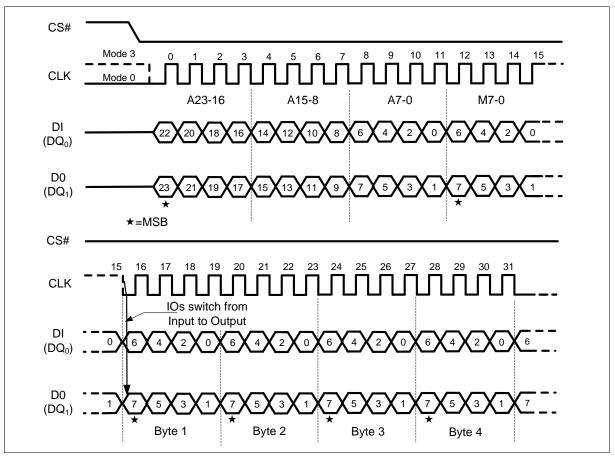

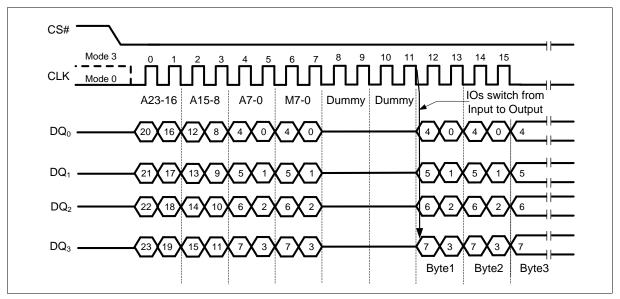

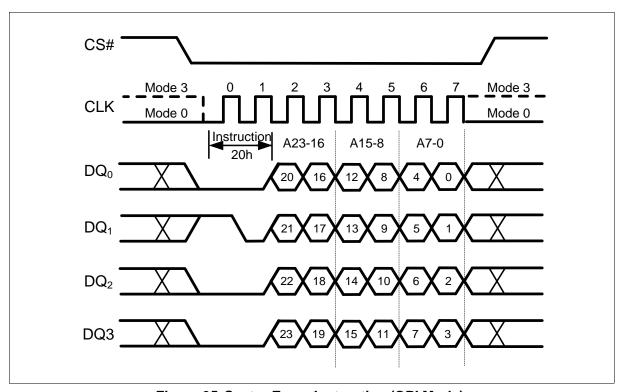

# 11.16. Fast Read Quad I/O (EBh)

The Fast Read Quad I/O (EBh) instruction is similar to the Fast Read Dual I/O (BBh) instruction except that address and data bits are input and output through four pins DQ<sub>0</sub>, DQ<sub>1</sub>, DQ<sub>2</sub> and DQ<sub>3</sub> and four Dummy clocks are required in SPI mode prior to the data output. The Quad I/O dramatically reduces instruction overhead allowing faster random access for code execution (XIP) directly from the Quad SPI. The Quad Enable bit (QE) of Status Register-2 must be set to enable the Fast Read Quad I/O Instruction.

### Fast Read Quad I/O with "Continuous Read Mode"

The Fast Read Quad I/O instruction can further reduce instruction overhead through setting the "Continuous Read Mode" bits (M7-0) after the input Address bits A23-A0, as shown in Figure 23. The upper nibble of the (M7-4) controls the length of the next Fast Read Quad I/O instruction through the inclusion or exclusion of the first byte instruction code. The lower nibble bits of the (M3-0) are don't care ("x"). However, the DQ pins should be high-impedance prior to the falling edge of the first data out clock.

If the "Continuous Read Mode" bits M5-4 = (1,0), then the next Fast Read Quad I/O instruction (after CS# is raised and then lowered) does not require the EBh instruction code, as shown in Figure 24. This reduces the instruction sequence by eight clocks and allows the Read address to be immediately entered after CS# is asserted low. If the "Continuous Read Mode" bits M5-4 do not equal to (1,0), the next instruction (after CS# is raised and then lowered) requires the first byte instruction code, thus returning to normal operation. It is recommended to input FFh on DQ0 for the next instruction (8 clocks), to ensure M4 = 1 and return the device to normal operation.

Figure 23 Fast Read Quad I/O Instruction (Initial instruction or previous M5-4≠10, SPI Mode)

Figure 24 Fast Read Quad I/O Instruction (Previous instruction set M5-4 = 10, SPI Mode)

### Fast Read Quad I/O with "8/16/32/64-Byte Wrap Around" in Standard SPI mode

The Fast Read Quad I/O instruction can also be used to access a specific portion within a page by issuing a "Set Burst with Wrap" (77h) command prior to EBh. The "Set Burst with Wrap" (77h) command can either enable or disable the "Wrap Around" feature for the following EBh commands. When "Wrap Around" is enabled, the data being accessed can be limited to either a 8, 16, 32 or 64-byte section of a 256-byte page. The output data starts at the initial address specified in the instruction, once it reaches the ending boundary of the 8/16/32/64-byte section, the output will wrap around to the beginning boundary automatically until CS# is pulled high to terminate the command.

The Burst with Wrap feature allows applications that use cache to quickly fetch a critical address and then fill the cache afterwards within a fixed length (8/16/32/64-byte) of data without issuing multiple read commands.

The "Set Burst with Wrap" instruction allows three "Wrap Bits", W6-4 to be set. The W4 bit is used to enable or disable the "Wrap Around" operation while W6-5 are used to specify the length of the wrap around section within a page. See "11.19 Set Burst with Wrap (77h)" for detail descriptions.

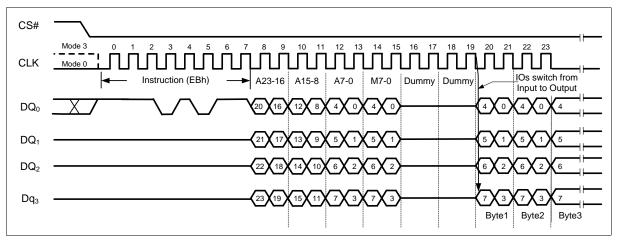

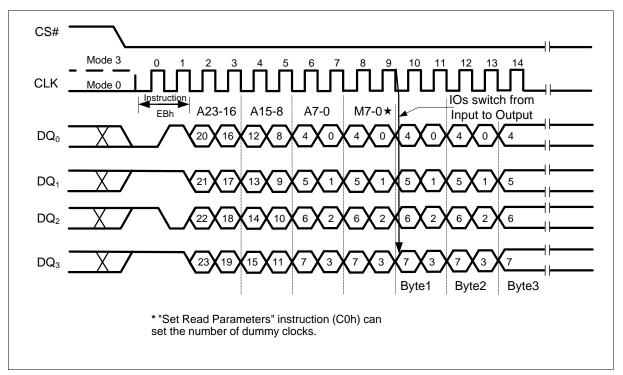

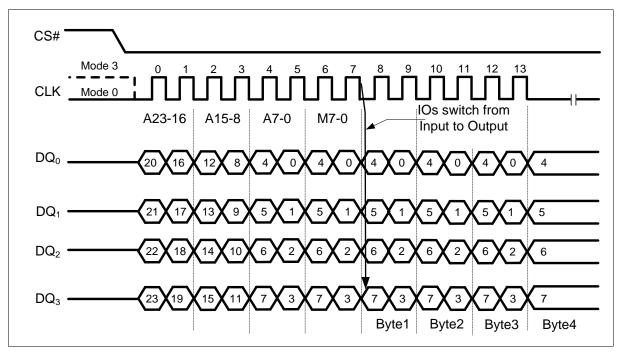

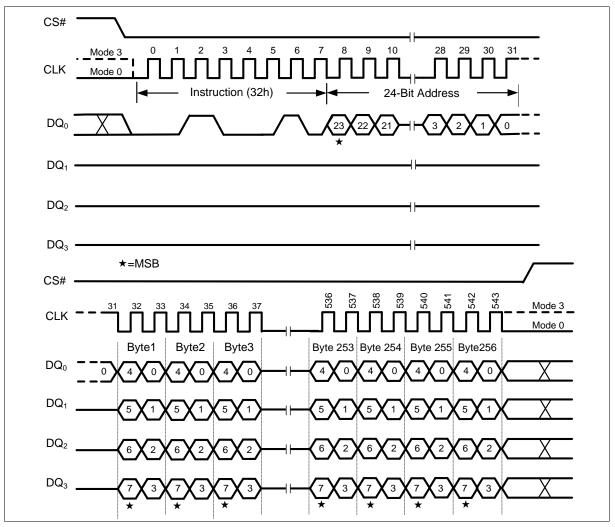

### Fast Read Quad I/O (EBh) in QPI Mode

The Fast Read Quad I/O instruction is also supported in QPI mode, as shown in Figure 25. When QPI mode is enabled, the number of dummy clocks is configured by the "Set Read Parameters (C0h)" instruction to accommodate a wide range application with different needs for either maximum Fast Read frequency or minimum data access latency. Depending on the Read Parameter Bits P[5:4] setting, the number of dummy clocks can be configured as either 2, 4, 6 or 8. The default number of dummy clocks upon power up or after a Reset instruction is 2. In QPI mode, the "Continuous Read Mode" bits M7-0 are also considered as dummy clocks. In the default setting, the data output will follow the Continuous Read Mode bits immediately.

"Continuous Read Mode" feature is also available in QPI mode for Fast Read Quad I/O instruction. Please refer to the description on previous pages.

"Wrap Around" feature is not available in QPI mode for Fast Read Quad I/O instruction. To perform a read operation with fixed data length wrap around in QPI mode, a dedicated "Burst Read with Wrap" (0Ch) instruction must be used. Please refer to "11.38 Burst Read with Wrap (0Ch)" for details.

Figure 25 Fast Read Quad I/O Instruction (Initial instruction or previous M5-4≠10, QPI Mode)

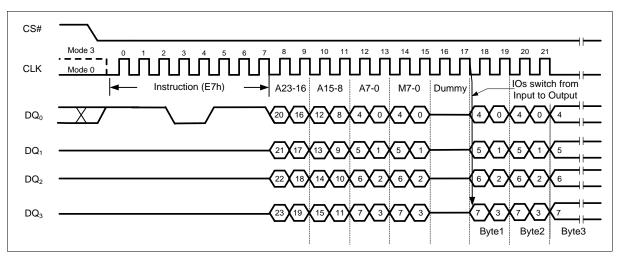

# 11.17. Word Read Quad I/O (E7h)

The Word Read Quad I/O (E7h) instruction is similar to the Fast Read Quad I/O (EBh) instruction except that the lowest Address bit (A0) must equal 0 and only two Dummy clock are required prior to the data output. The Quad I/O dramatically reduces instruction overhead allowing faster random access for code execution (XIP) directly from the Quad SPI. The Quad Enable bit (QE) of Status Register-2 must be set to enable the Word Read Quad I/O Instruction.

### Word Read Quad I/O with "Continuous Read Mode"

The Word Read Quad I/O instruction can further reduce instruction overhead through setting the "Continuous Read Mode" bits (M7-0) after the input Address bits A23-A0, as shown in Figure 26.

The upper nibble of the (M7-4) controls the length of the next Fast Read Quad I/O instruction through the inclusion or exclusion of the first byte instruction code. The lower nibble bits of the (M3-0) are don't care ("x"). However, the DQ pins should be high-impedance prior to the falling edge of the first data out clock.